Xilinx FIR Compiler 5.0: 设计高效FIR滤波器IP核指南

需积分: 46 148 浏览量

更新于2024-07-23

收藏 2MB PDF 举报

"FIR Compiler 5.0 是Xilinx公司提供的一个LogiCORE IP核心,用于在FPGA设计中生成高度可配置、高效且节省面积的高性能FIR滤波器。该工具支持用户通过Multiply-Accumulate (MAC)或Distributed Arithmetic (DA)架构来实现FIR滤波器。它兼容多种Xilinx FPGA系列,包括Kintex-7、Virtex-7、Virtex-6、Virtex-5、Virtex-4、Spartan-6以及Spartan-3系列。"

FIR Compiler 5.0的核心特性包括:

1. **通用模块**:FIR Compiler作为一个即插即用的模块,可以方便地集成到基于Kintex-7、Virtex-7等指定系列的FPGA设计中,为用户提供了极大的灵活性。

2. **高性能滤波器**:该工具支持多种类型的高性能FIR滤波器,包括但不限于:

- **有限脉冲响应(FIR)滤波器**:FIR滤波器是一种线性相位滤波器,具有可编程的频率响应,适用于多种信号处理应用。

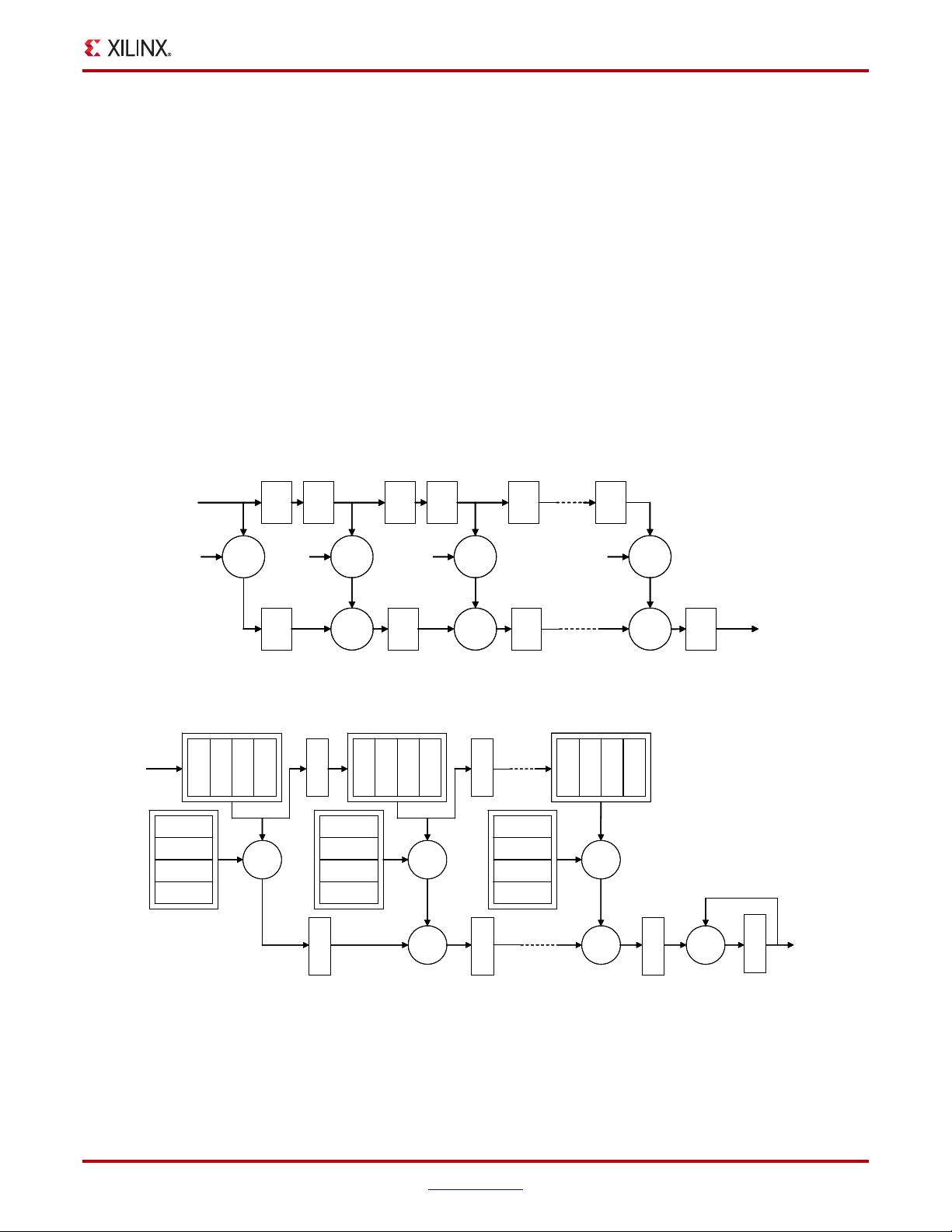

- **多相解码器**:这种滤波器可以降低输入信号的采样率,有助于减少数据带宽需求。

- **多相插值器**:相反,它可以增加采样率,提高信号分辨率。

- **半带滤波器**:半带滤波器是一种特殊的FIR滤波器,主要用于信号的下采样或上采样,可以有效地减半或加倍信号的采样率。

- **希尔伯特变换器**:希尔伯特变换可以提供信号的瞬时幅度和相位信息。

- **多相滤波器银行**:多相滤波器银行用于实现多通道信号处理,如频谱分析或解调。

- **插值滤波器**:这种滤波器在信号插值过程中起作用,能够平滑信号并减少高频噪声。

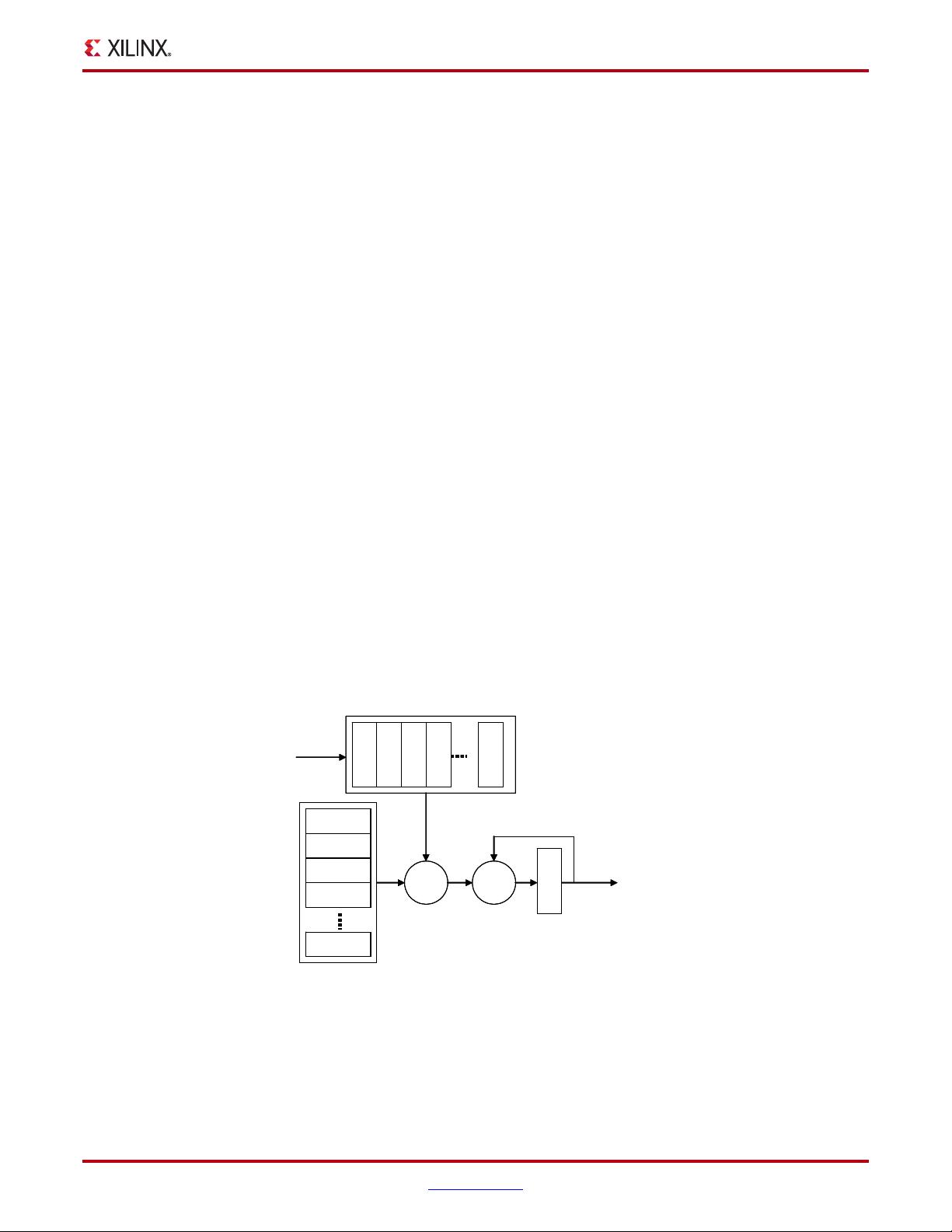

3. **架构选择**:用户可以选择使用MAC或DA架构来实现滤波器。MAC架构是基于乘法和累加操作的经典方法,而DA架构则通过分布式运算来减少硬件资源的使用,提高速度或效率。

4. **参数化设计**:FIR Compiler允许用户根据具体应用需求调整滤波器参数,如阶数、滚降率、截止频率等,以优化性能和资源利用率。

5. **知识产权(IP)保护**:Xilinx作为知识产权供应商,其商标和品牌受到法律保护,确保了产品的质量和可靠性。

FIR Compiler 5.0是一个强大的工具,为设计者提供了构建高性能FIR滤波系统的能力,适用于通信、音频处理、图像处理等多个领域。通过灵活的架构选择和丰富的滤波器类型,用户可以根据项目需求定制适合的解决方案,同时确保在FPGA上实现高效、节省资源的硬件实现。

2021-01-20 上传

2013-03-21 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

2023-07-29 上传

2011-03-25 上传

ljj0709

- 粉丝: 0

- 资源: 1