FPGA复位陷阱与同步异步策略解析

需积分: 5 45 浏览量

更新于2024-10-26

收藏 534KB DOC 举报

FPGA复位技术是FPGA设计中至关重要的一步,但由于其复杂性常被设计师忽视,从而可能导致难以诊断的设计问题。本文旨在深入探讨FPGA复位的正确实践,特别是异步复位与同步复位的区别及其潜在问题。

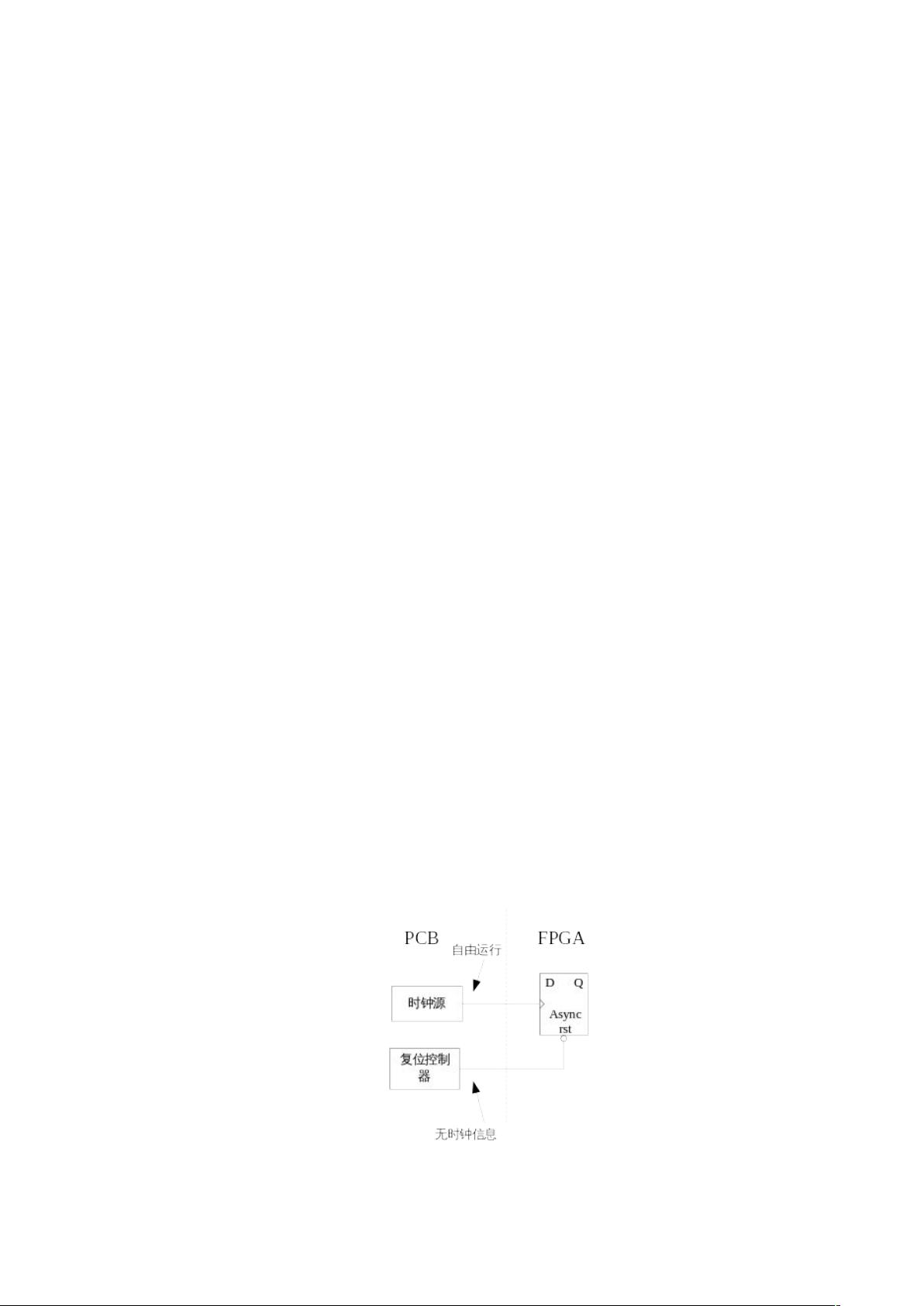

异步复位是一种常见的复位方式,它通过一条独立的复位信号线(rst_n)直接控制触发器的复位输入。这种复位没有依赖于系统时钟,复位操作和释放会在无时钟条件下执行。例如,图1中的`resetff`模块展示了异步复位的基本结构,触发器在接收到rst_n下降沿时复位,而在rst_n变为高电平时复位解除。然而,当模块边界与整个FPGA的边界重合时,复位控制会变得更复杂,如图2所示,上电期间需要监控电压电平以确保在适当的时间释放复位。

然而,异步复位的一个主要挑战是复位恢复时间(Reset Recovery Time,RRT),即从复位信号解除到触发器完全恢复到稳定状态所需的时间。如果复位释放时间与时钟周期不匹配,如图3所示,可能会导致输出端的不稳定性和不可预测行为,因为复位恢复条件未被正确满足。

为解决这个问题,同步复位应运而生。同步复位(如图4所示)将复位信号与系统时钟同步,确保复位操作始终发生在时钟的上升沿,这样可以避免复位恢复时间冲突。同步复位的优势在于它能保证所有触发器的复位过程一致且符合时序要求,从而确保系统的稳定性。然而,同步复位的缺点是复位信号可能需要更长的时间来传播到所有单元,这可能导致“毛刺”或“无效时钟域交叉”。

在实际设计中,选择异步还是同步复位取决于具体的应用场景。对于实时性要求高的系统,异步复位可能更为合适;而对于对时序一致性要求严格的系统,同步复位则是更好的选择。设计者需要仔细权衡,确保复位逻辑的正确性和系统性能。参考文献《Advanced FPGA Design Architecture, Implementation, and Optimization》和《Advanced Digital Design with the Verilog HDL》提供了深入理解和实施复位技术的宝贵资源。在整个设计过程中,良好的复位策略是降低设计风险和提高整体系统可靠性的关键。

209 浏览量

195 浏览量

181 浏览量

1145 浏览量

309 浏览量

134 浏览量

165 浏览量

199 浏览量

104 浏览量

wanjaw

- 粉丝: 0

最新资源

- 技术顾问的TFIPreWork项目介绍与实践

- 深入理解JAVA数据结构与算法

- 深入分析BPM测试工具:MixMeister BPM Analyzer

- 项目31:PROC41-模板的JavaScript应用实例

- 中国交通标志CTSDB数据集12: 800个图像与文本训练样本

- 学习心得记录与思路分享

- 利用ASP.NET SignalR打造实时聊天室教程

- Oracle数据库用户管理技巧与工具解析

- EasyUI界面组件模板代码大全

- 网页及C#表单设计通用小图标资源分享

- Prefab.js:掌握JavaScript中的原型继承技术

- Spring MVC与Redis、MyBatis及JDBC集成教程

- 基于STM32的互补滤波姿态解算技术

- Java平台的ModcraftWin模组开发工具介绍

- ISR算法在GWAS和上位性检测中的应用与优势分析

- 掌握编码面试技巧:LeetCode交互式挑战分析