Functional Overview

21

December 2004 − Revised September 2006 SGUS053B

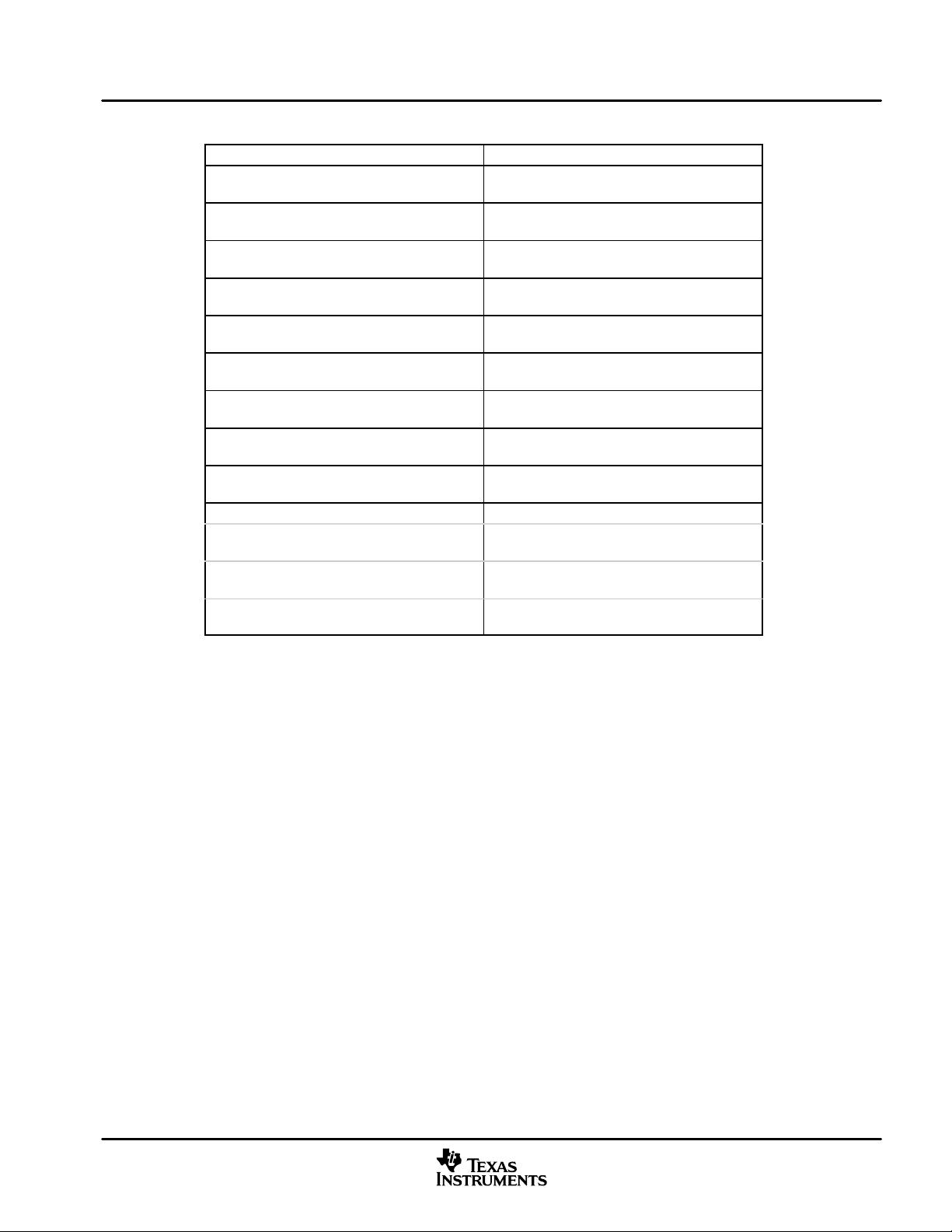

3.2.6 Flash

The F2812 contains 128K x 16 of embedded flash memory, segregated into four 8K X 16 sectors, and six 16K

X 16 sectors. The F2810 has 64K X 16 of embedded flash, segregated into two 8K X 16 sectors, and three

16K X 16 sectors. The device also contains a single 1K x 16 of OTP memory at address range 0x3D 7800

− 0x3D 7BFF. The user can individually erase, program, and validate a flash sector while leaving other sectors

untouched. However, it is not possible to use one sector of the flash or the OTP to execute flash algorithms

that erase/program other sectors. Special memory pipelining is provided to enable the flash module to achieve

higher performance. The flash/OTP is mapped to both program and data space; therefore, it can be used to

execute code or store data information.

NOTE:

The F2812 Flash and OTP wait states can be configured by the application. This allows

applications running at slower frequencies to configure the flash to use fewer wait states.

Flash effective performance can be improved by enabling the flash pipeline mode in the Flash

options register. With this mode enabled, effective performance of linear code execution is

much faster than the raw performance indicated by the wait state configuration alone. The

exact performance gain when using the Flash pipeline mode is application-dependent. The

pipeline mode is not available for the OTP block.

For more information on the Flash options, Flash wait-state, and OTP wait-state registers, see

the TMS320x281x System Control and Interrupts Reference Guide (SPRU078).

3.2.7 L0, L1, H0 SARAMs

The F281x contains an additional 16K x 16 of single-access RAM, divided into three blocks (4K + 4K + 8K).

Each block can be independently accessed hence minimizing pipeline stalls. Each block is mapped to both

program and data space.

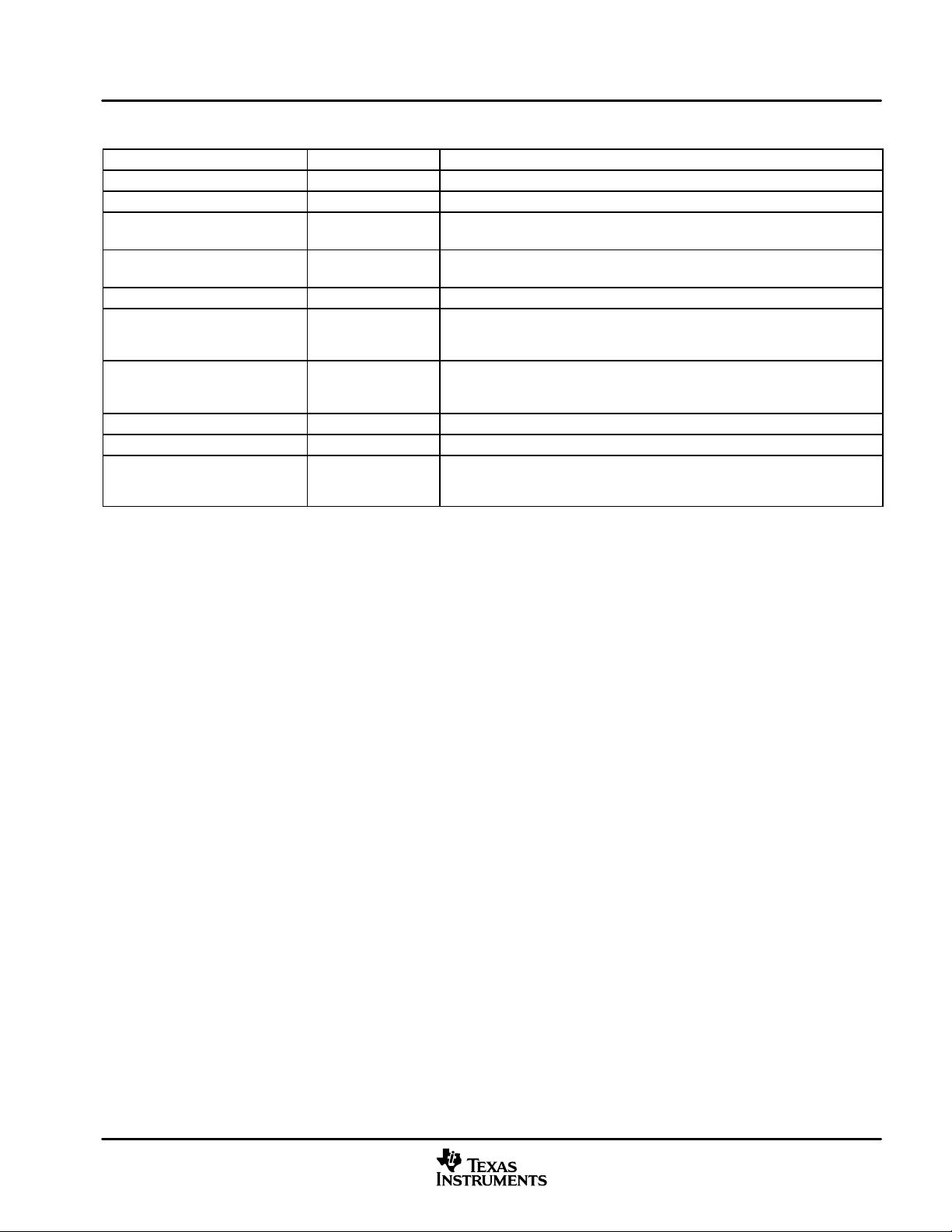

3.2.8 Boot ROM

The Boot ROM is factory-programmed with boot-loading software. The Boot ROM program executes after

device reset and checks several GPIO pins to determine which boot mode to enter. For example, the user can

select to execute code already present in the internal Flash or download new software to internal RAM through

one of several serial ports. Other boot modes exist as well. The Boot ROM also contains standard tables, such

as SIN/COS waveforms, for use in math-related algorithms. Table 3−3 shows the details of how various boot

modes may be invoked. See the TMS320x281x DSP Boot ROM Reference Guide (SPRS095), for more

information.

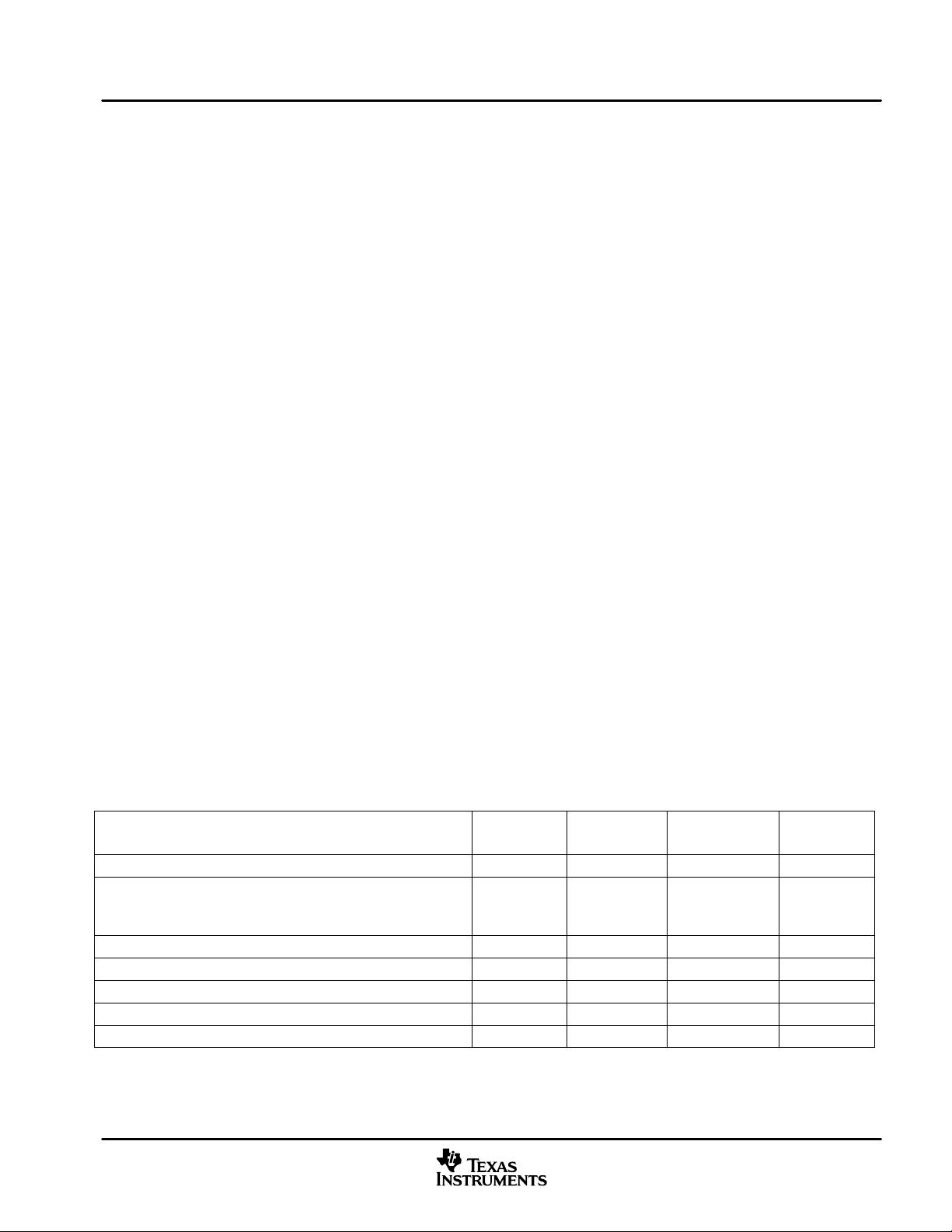

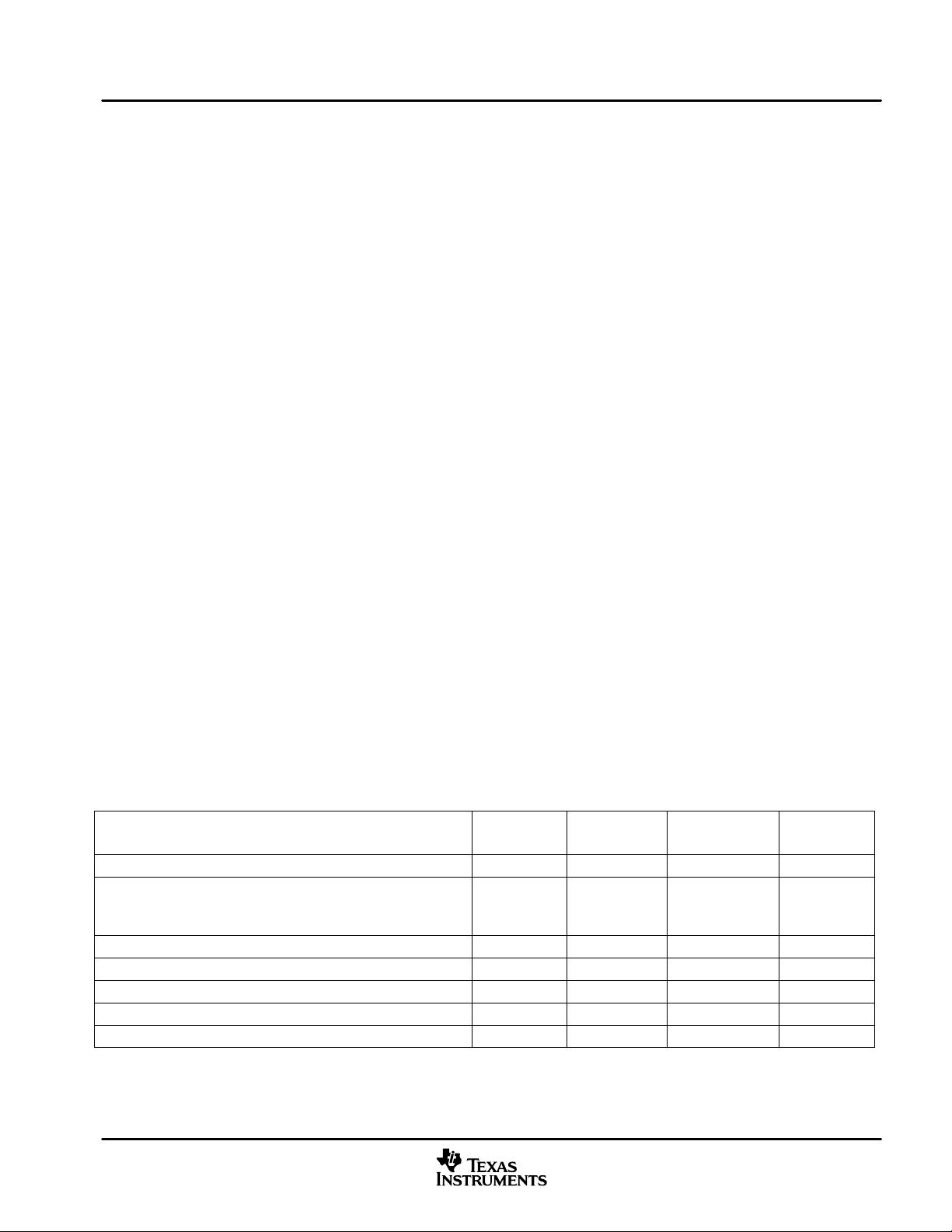

Table 3−3. Boot Mode Selection

BOOT MODE SELECTED

GPIOF4

(SCITXDA)

GPIOF12

(MDXA)

GPIOF3

(SPISTEA)

GPIOF2

(SPICLK)

GPIO PU status

†

PU No PU No PU No PU

Jump to Flash/ROM address 0x3F 7FF6

A branch instruction must have been programmed here prior to

reset to redirect code execution as desired.

1 x x x

Call SPI_Boot to load from an external serial SPI EEPROM 0 1 x x

Call SCI_Boot to load from SCI-A 0 0 1 1

Jump to H0 SARAM address 0x3F 8000 0 0 1 0

Jump to OTP address 0x3D 7800 0 0 0 1

Call Parallel_Boot to load from GPIO Port B 0 0 0 0

†

PU = pin has an internal pullup. No PU = pin does not have an internal pullup

‡

Extra care must be taken due to any effect toggling SPICLK to select a boot mode may have on external logic.

§

If the boot mode selected is Flash, H0, or OTP, then no external code is loaded by the bootloader.