阵列乘法器设计:加速乘法运算的实现方法

需积分: 50 39 浏览量

更新于2024-07-30

1

收藏 754KB DOC 举报

"阵列乘法器的设计"

这篇课程设计报告详细阐述了阵列乘法器的设计过程,旨在提高乘法运算的速度。阵列乘法器是通过类似人工计算的方法,利用电路阵列来实现快速的乘法操作。报告中提到了四位阵列乘法器,这种设计能够显著提升计算效率,尤其对于需要大量乘法运算的应用来说。

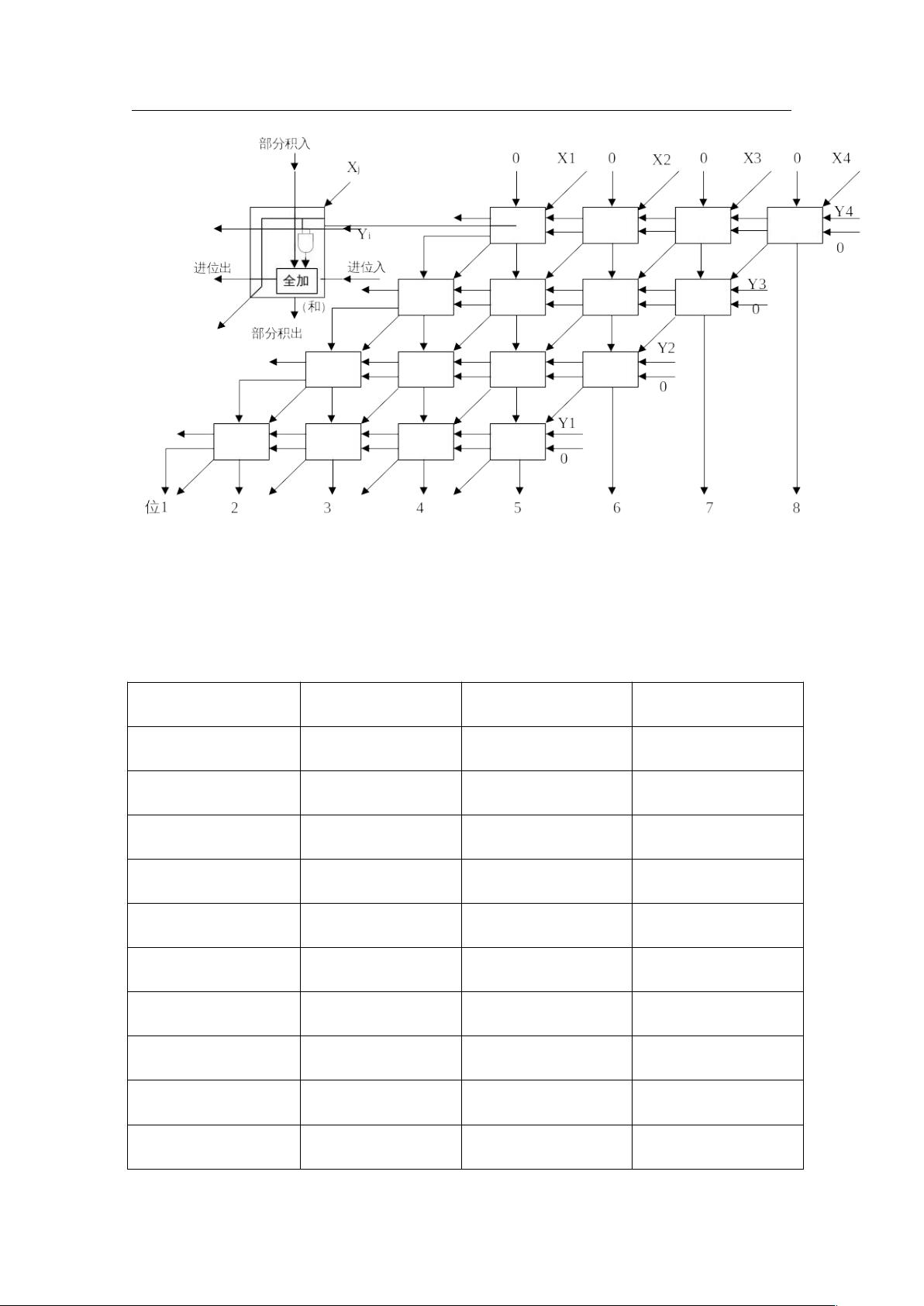

在第一章总体设计方案中,报告解释了设计原理。阵列乘法器基于被乘数和乘数的每一位进行逐位相乘,然后通过加法器将这些乘积相加得到最终结果。具体来说,四个被乘数输入端(X1, X2, X3, X4)和四个乘数输入端(Y1, Y2, Y3, Y4)对应于被乘数和乘数的每一位,乘积输出端(M0, M1, ..., M7)则输出乘积的各个位。每行对应乘数的一位,而斜列对应被乘数的位,这样就形成了一个矩阵结构,使得乘法运算并行进行。

第二章详细设计方案中,报告进一步分解了设计步骤。首先,创建了顶层图形设计文件,并选择了合适的器件及引脚锁定。接着,报告详细描述了功能模块的设计,包括四位阵列乘法模块和细胞模块。四位阵列乘法模块由多个加法器组成,每个加法器由一个与门和一个全加器构建。全加器是阵列乘法器的核心单元,它能处理两个数的相加并考虑进位。细胞模块则是阵列乘法器的基础单元,它们组合在一起实现了阵列结构。这部分还涉及到仿真调试,以确保设计的正确性。

第三章则讨论了编程下载与硬件测试的过程。设计的原理图经过编译和调试后,生成了*.bit文件,这个文件被下载到XCV200可编程逻辑芯片中。硬件测试是验证设计是否符合预期的关键步骤,通过对输入和输出进行实际操作,分析测试结果,确保阵列乘法器能正确执行乘法运算。

报告中的四位阵列乘法器功能表给出了具体的输入和输出示例,表明设计的电路应当能够正确地处理不同输入组合下的乘法操作。

这份报告详尽地介绍了阵列乘法器的原理、设计方法和实现过程,包括了从高层次的系统设计到低层次的逻辑门实现,以及最后的硬件验证。这样的设计对于理解数字逻辑电路、计算机组成原理以及硬件设计流程有着重要的教育意义。

1859 浏览量

175 浏览量

617 浏览量

3291 浏览量

2021-03-24 上传

119 浏览量

点击了解资源详情

2080 浏览量

yanick006

- 粉丝: 0

最新资源

- 深入解析JavaWeb中Servlet、Jsp与JDBC技术

- 粒子滤波在视频目标跟踪中的应用与MATLAB实现

- ISTQB ISEB基础级认证考试BH0-010题库解析

- 深入探讨HTML技术在hundeakademie中的应用

- Delphi实现EXE/DLL文件PE头修改技术

- 光线追踪:探索反射与折射模型的奥秘

- 构建http接口以返回json格式,使用SpringMVC+MyBatis+Oracle

- 文件驱动程序示例:实现缓存区读写操作

- JavaScript顶盒技术开发与应用

- 掌握PLSQL: 从语法到数据库对象的全面解析

- MP4v2在iOS平台上的应用与编译指南

- 探索Chrome与Google Cardboard的WebGL基础VR实验

- Windows平台下的IOMeter性能测试工具使用指南

- 激光切割板材表面质量研究综述

- 西门子200编程电缆PPI驱动程序下载及使用指南

- Pablo的编程笔记与机器学习项目探索