门控时钟技术在低功耗设计中的应用

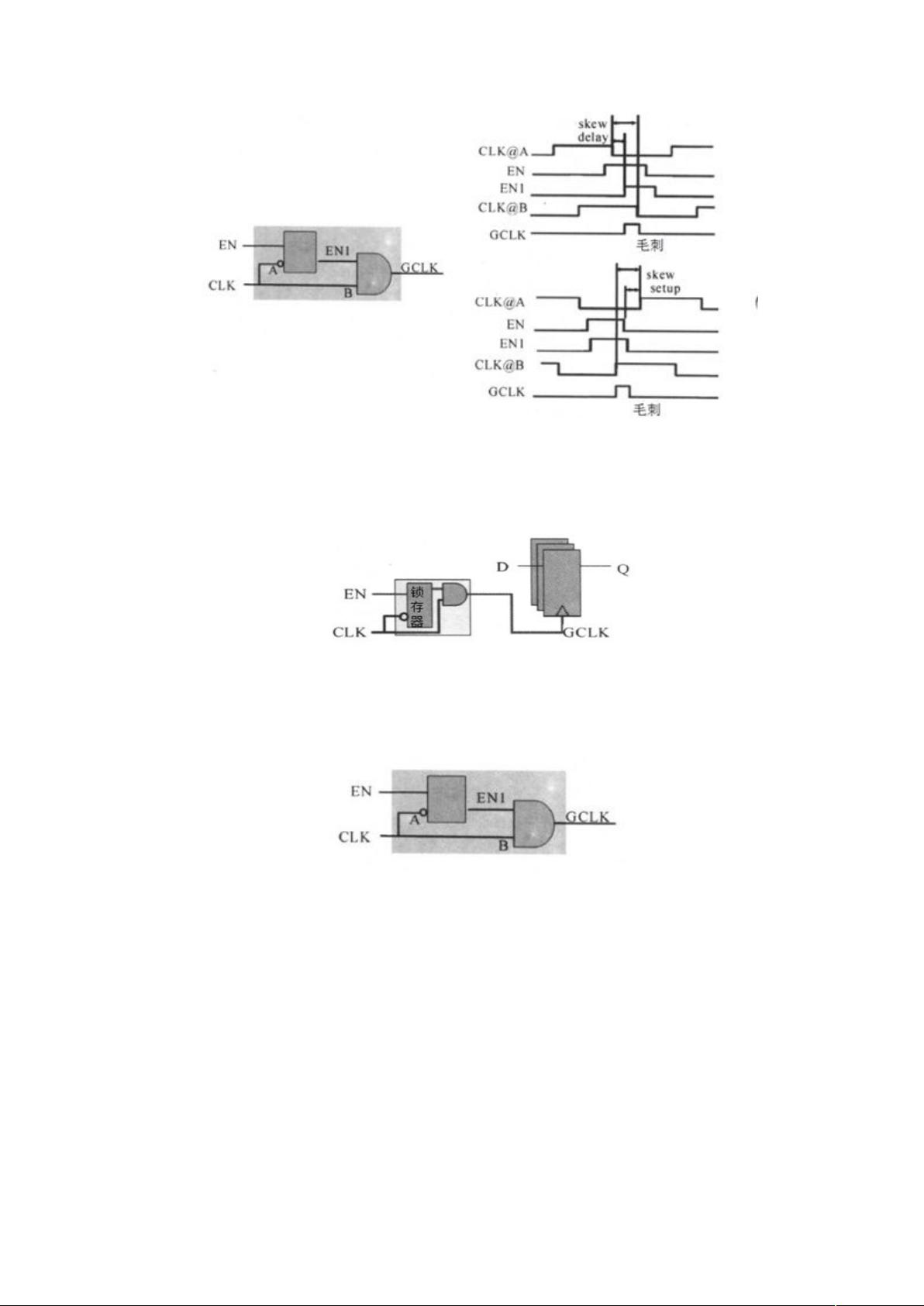

"低功耗之门控时钟设计是数字集成电路设计中的一种重要技术,用于降低芯片的功耗。门控时钟通过在不需要时关闭时钟信号,减少无谓的逻辑翻转,进而减少动态功耗。文章主要讨论了门控时钟的概念、类型、应用以及综合库中的实现方式。" 门控时钟设计是数字集成电路(数字IC)中实现低功耗的关键策略之一。在现代半导体技术中,随着晶体管尺寸的缩小,静态功耗和动态功耗成为设计者必须考虑的重要因素。动态功耗主要来源于时钟驱动逻辑门时的电荷充放电,而门控时钟设计就是针对这一问题提出的解决方案。 门控时钟的基本原理是通过一个控制信号来决定是否允许时钟信号到达特定的寄存器或模块。当该部分电路不需要活动时,关闭时钟,可以显著降低动态功耗,通常能节省20%-60%的功耗,并且减少不必要的门控逻辑,从而节省面积。门控时钟的应用有两种主要形式:寄存器级和模块级,寄存器级的门控更为灵活,因为它可以直接针对单个寄存器进行优化。 门控时钟单元有两类:带锁存器(latch-based)和不带锁存器(latch-free)。带锁存器的门控时钟单元能防止毛刺,因此更加安全,但可能会引入额外的延迟。不带锁存器的门控时钟单元则可能在某些情况下产生不稳定的行为。 在实际设计中,门控时钟可以采用离散的CG单元或者集成的CG单元(如ICG)。离散的CG单元包括使用与门或或门作为门控逻辑,但这些方法可能会引入毛刺问题。相比之下,集成的CG单元(如Synopsys的ICG)提供了更优化的解决方案,可以更好地管理和控制时钟使能信号,以确保时钟信号的干净切换,同时减少毛刺的产生。 在综合阶段,设计者可以使用工具(如Synopsys的Design Compiler)的特定选项(如`set_clock_gating_style`)来指定使用哪种类型的门控时钟单元。通过这种方式,设计者能够在RTL编码阶段就考虑到低功耗设计,使得综合工具能够自动映射到相应的门控时钟结构。 门控时钟设计是数字IC设计中不可或缺的一部分,它通过精细的时钟管理,有效地降低了功耗,提高了能效,对于移动设备和物联网等对功耗敏感的应用尤为重要。设计者需要理解门控时钟的工作原理、选择合适的门控单元类型,并在设计流程早期就考虑低功耗策略,以确保最终产品的性能和功耗达到最优平衡。

剩余17页未读,继续阅读

- 粉丝: 2

- 资源: 1

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- Lombok 快速入门与注解详解

- SpringSecurity实战:声明式安全控制框架解析

- XML基础教程:从数据传输到存储解析

- Matlab实现图像空间平移与镜像变换示例

- Python流程控制与运算符详解

- Python基础:类型转换与循环语句

- 辰科CD-6024-4控制器说明书:LED亮度调节与触发功能解析

- AE particular插件全面解析:英汉对照与关键参数

- Shell脚本实践:创建tar包、字符串累加与简易运算器

- TMS320F28335:浮点处理器与ADC详解

- 互联网基础与结构解析:从ARPANET到多层次ISP

- Redhat系统中构建与Windows共享的Samba服务器实战

- microPython编程指南:从入门到实践

- 数据结构实验:顺序构建并遍历链表

- NVIDIA TX2系统安装与恢复指南

- C语言实现贪吃蛇游戏基础代码

信息提交成功

信息提交成功