Verilog综合过程解析:从RTL到门级网表

78 浏览量

更新于2024-08-28

收藏 616KB PDF 举报

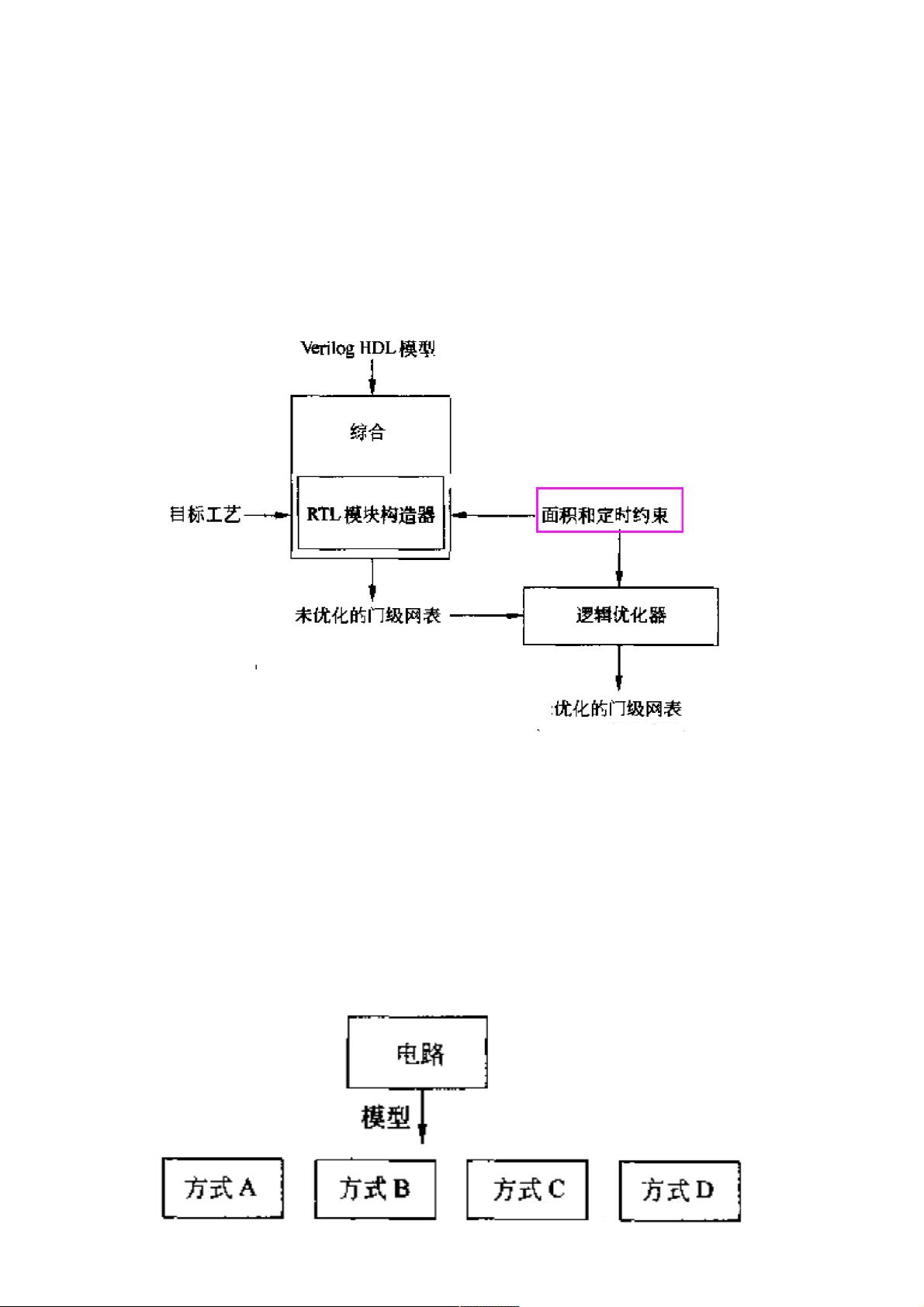

"Verilog设计流程中的综合是一个关键步骤,它将RTL级的Verilog描述转化为门级网表,为后续的布局与布线做准备。这个过程中,综合器使用预定义元件库中的模块来构造目标工艺所需的硬件功能。综合后的网表文件包含了各种基本逻辑单元,如触发器、ALUs和多路选择器等。综合还涉及到逻辑优化,以满足面积和定时约束。某些Verilog特性,如系统任务和特定语句,是不可综合的,仅用于仿真。综合器之间的差异可能导致相同设计在不同工具下的不可移植性。在FPGA开发流程中,综合处于代码编写、仿真和实现之间。"

在Verilog设计流程中,综合是一个至关重要的环节。它将用VerilogHDL编写的高级抽象电路模型转换为实际的门级表示,这个模型通常是在寄存器传输级(RTL)描述的。RTL级的描述允许设计者以更接近硬件行为的方式表达电路,而不必关心底层的具体实现细节。Verilog提供了在门级、RTL级以及行为级描述硬件的能力,而VHDL则更偏向于系统级别的描述。

综合过程涉及多个步骤。首先,RTL模块构造器根据设计者的Verilog代码和目标工艺,从元件库中选择或生成适合的功能模块。这些模块包括基础的数字逻辑元件,如D触发器、加法器、乘法器和多路选择器等。生成的门级网表是一个逻辑连接这些基本元件的结构。

接下来,逻辑优化器对网表进行处理,依据面积和定时约束进行优化。这一步骤旨在减小芯片面积、提高速度或满足其他设计要求。优化可能包括逻辑简化、门级替换和路径调整等操作。

然而,并非所有的Verilog特性都是可综合的。例如,系统任务如`$display()`和`initial`语句用于仿真,无法转换为硬件元件,因此在综合时会被忽略。此外,由于不同综合器对Verilog语法的支持程度不同,一个在某种综合器上可综合的设计可能在另一个综合器上不可综合,这可能导致设计的不兼容性。

设计流程通常包括编写代码、仿真验证、综合、布局与布线以及最终的配置。在开发过程中,理解特定综合器的限制和语法是非常重要的,以确保编写出完全可综合的Verilog代码。

映射机制是综合的核心部分,它决定了如何将RTL描述映射到门级元素。这涉及到解析Verilog代码,识别逻辑操作和数据流,然后将它们转换为逻辑门。例如,逻辑操作符(如`&`和`|`)会被转换为与门和或门,而移位操作可能会映射到一系列的移位寄存器。此外,综合器还会考虑时钟路径、同步和异步信号处理,以及如何构建存储元件如触发器和锁存器。

Verilog的综合过程是一个复杂而关键的步骤,它连接了设计的高层次抽象和实际的硬件实现,同时也受到综合工具特性和设计约束的影响。理解这一过程对于有效地利用Verilog进行数字系统设计至关重要。

296 浏览量

点击了解资源详情

点击了解资源详情

106 浏览量

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

weixin_38723810

- 粉丝: 9

- 资源: 881

最新资源

- rtl8761b_bluetooth5.0_linux_driver.7z

- STRIPE-INTEGRATION

- 3D Shepp-Logan Phantom:Matlab 的 phantom() 的 3D 扩展-matlab开发

- Clementine-Vulgate

- 区域业务周报表excel模版下载

- Batua:个人应用程序,用于跟踪和管理您的费用

- 中式餐厅包间模型设计

- platform_device_xiaomi_violet

- Valcolor:将颜色 CLR 应用于与值 VAL 相关的颜色图条目。 缩放或索引图。-matlab开发

- 517-面包房

- winform窗体、控件的简单封装,重做标题栏

- xaiochengxu-learn:小程序

- 企业-迪普科技-2020年年终总结.rar

- 工作日报excel模版下载

- MyLaya

- Regression_09.05.20:这是一系列代码,用于导入数据,进行回归分析,居中变量和可视化交互