Verilog设计流程中综合的作用和限制

17 浏览量

更新于2024-08-28

收藏 613KB PDF 举报

Verilog设计流程:综合

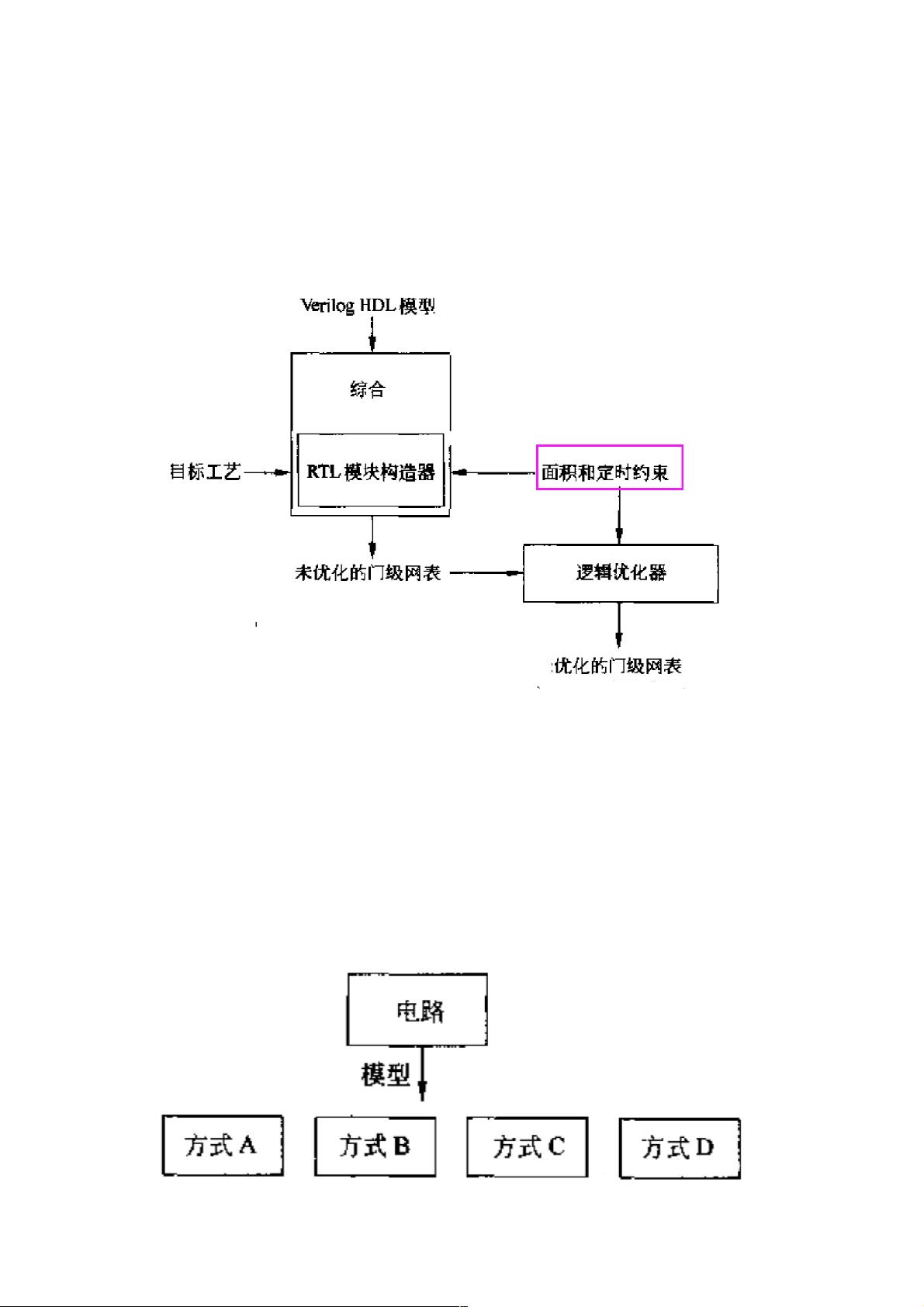

Verilog设计流程中的综合阶段是将Verilog描述的RTL级电路模型构造出门级网表的过程。该过程是将高级描述语言转换为低级网表语言,以便于后续的逻辑优化和物理实现。

1.1 What is Synthesis?

VerilogHDL和VHDL都是硬件描述语言,可以在不同的抽象层次上对电路进行建模。VerilogHDL侧重于电路级,可以在门级和寄存器传输级(RTL)描述硬件,也可以在算法级对硬件加以描述。而VHDL侧重于系统级。综合就是将Verilog描述的RTL级电路模型构造出门级网表的过程。综合只是个中间步骤,综合后生成的网表文件,就是由导线相互连接的寄存器传输级功能块(像是触发器、算术逻辑单元和多路选择器等)组成的。

1.2 不可综合

HDL的描述有不同的抽象层次,从门级、RTL级、行为级以及算法级进行建模。但是,并不是所有层次上的描述方式都可以被综合成想要的硬件元件,即不可综合。比如Verilog中存在一些用于仿真验证的子集,属于仿真验证语言,只在仿真时候使用,不能被综合成电路,因为没有相应的硬件元件与其对应。

1.3 在设计流程中的位置?

不同的综合器支持的Verilog可综合的子集一般是不同的,而Verilog中不存在单个的对象来表示锁存器或触发器因此每一种综合器都会有自己的综合机制来实现锁存器或触发器的建模。在学习和使用的过程中,不仅要理解VerilogHDL而且还得理解特定综合器的建模方式,这样才可写入完全可综合的模型。

2. 映射机制

既然综合器能够将HDL语言转换成门级网表,那么综合器必定有一种映射机制来将高级描述语言转换为低级网表语言。这种映射机制是实现综合的关键步骤,使得设计人员可以更方便地设计和实现数字电路。

Verilog设计流程中的综合阶段是将高级描述语言转换为低级网表语言,以便于后续的逻辑优化和物理实现。设计人员需要理解VerilogHDL和特定综合器的建模方式,以便写入完全可综合的模型。

点击了解资源详情

106 浏览量

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

weixin_38711778

- 粉丝: 2

- 资源: 895

最新资源

- 行业文档-设计装置-一种平台及天线支架一体化通讯铁塔.zip

- voyager-在锈中爬行和刮擦网页-Rust开发

- 基于Python实现翻译功能.rar

- 两点间坡度标注.rar

- OCR识别图像并提取文字,生成二维码

- FinishedBasicProducer

- OpenROAD:OpenROAD的统一应用程序实现了RTL到GDS的流程

- poicrawl.7z

- systemsoft:SystemSoft AS官方网站

- 行业文档-设计装置-一种具有储能功能的空气能洗脸盆.zip

- DiaryBot-V2

- CvTest.zip

- matlab确定眼睛的代码-Facial-expression-and-eye-color-matlab:从这里获取代码:

- 后台轻量级建站包 v1.3

- 行业文档-设计装置-一种平台板与侧板组成立体段的焊接工艺.zip

- SmartDoorLock:这是Smart Door Lock Android应用程序的官方存储库