北京大学微处理器中心:VLIW/EPIC高级计算机系统结构与超标量技术详解

需积分: 0 89 浏览量

更新于2024-06-30

收藏 1.65MB PDF 举报

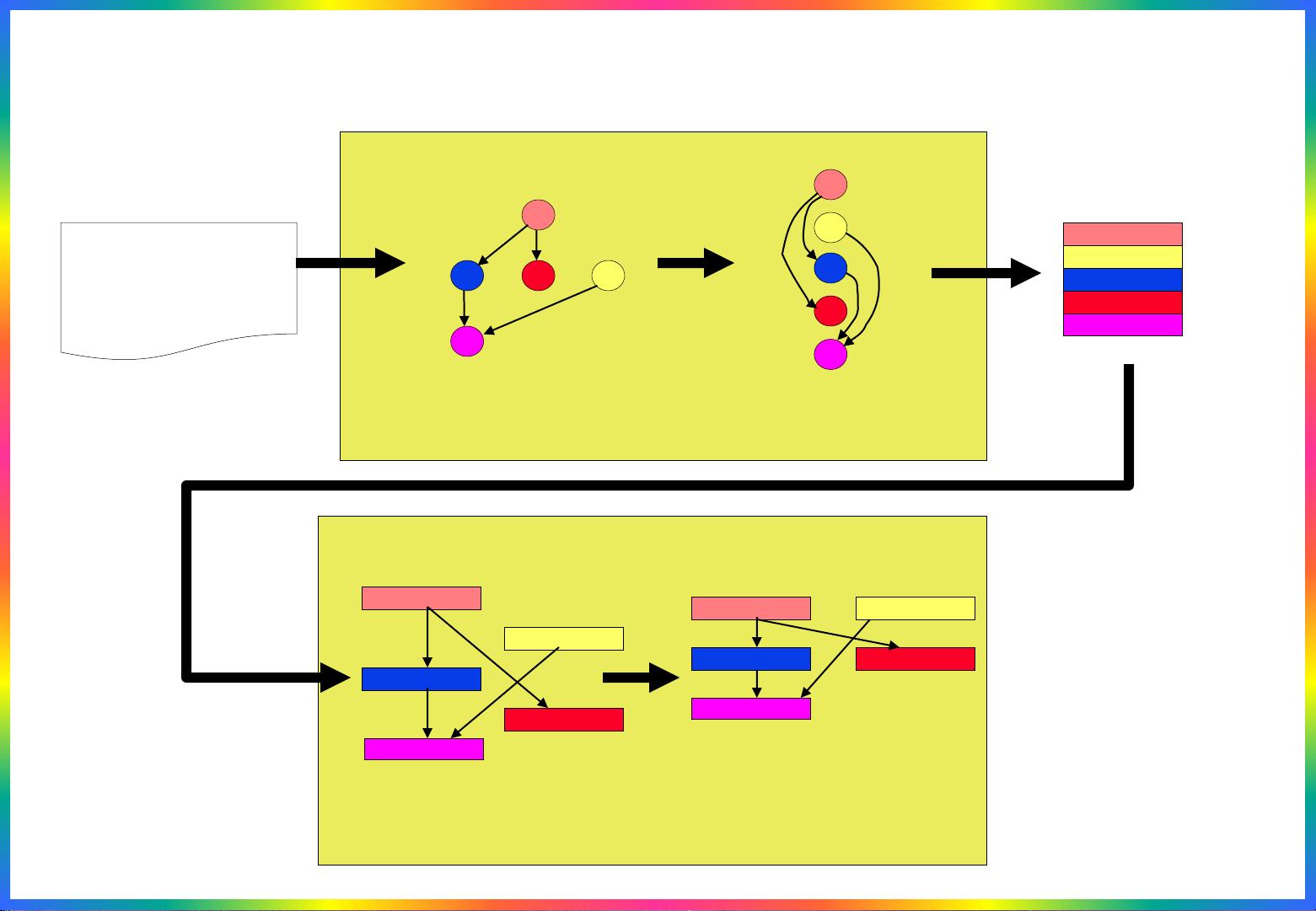

本课程是北京大学微处理器研究开发中心在2014年4月21日进行的高级计算机系统结构教学,由程旭教授主讲,主要围绕VLIW(Very Long Instruction Word)和EPIC(Explicitly Parallel Instruction Computing)架构展开,重点讨论了基于静态调度的指令级并行(Instruction-Level Parallelism, ILP)技术。VLIW设计允许一次执行多条指令,而EPIC则强调指令的明确并行性,通过预编译器将程序分解成并行执行的单元。

课程内容涵盖了多个关键组件和概念,例如:

1. Fetch and Decode:处理器首先从内存中获取指令,并进行解码,这是执行流程的基础。

2. Renaming:为了处理指令间的依赖关系,处理器可能需要对指令进行重命名,避免冲突,这在超标量架构中尤为重要。

3. Reorder Buffer (ROB):由于指令执行的乱序性,ROB负责调整指令执行顺序,确保正确性。

4. Branch Prediction:处理器使用预测器来预判分支指令的结果,如基于路径预测器能有效提高预测准确性,而 Branch Target Buffer (BTB) 和 Branch History Table (BHT) 在控制流管理中起着重要作用。

5. Pipeline Recovery:处理转移错误时,使用流水线快照来减少执行损失,确保系统稳定。

6. Register File Management:为了避免数据冲突,处理器采用了统一物理寄存器堆的设计,减少了跨存储区域的数据访问。

7. Superscalar Execution:超标量处理器可以同时执行多个指令,这要求处理器具备重命名、推测式存储缓冲器等功能,以克服存储操作延迟。

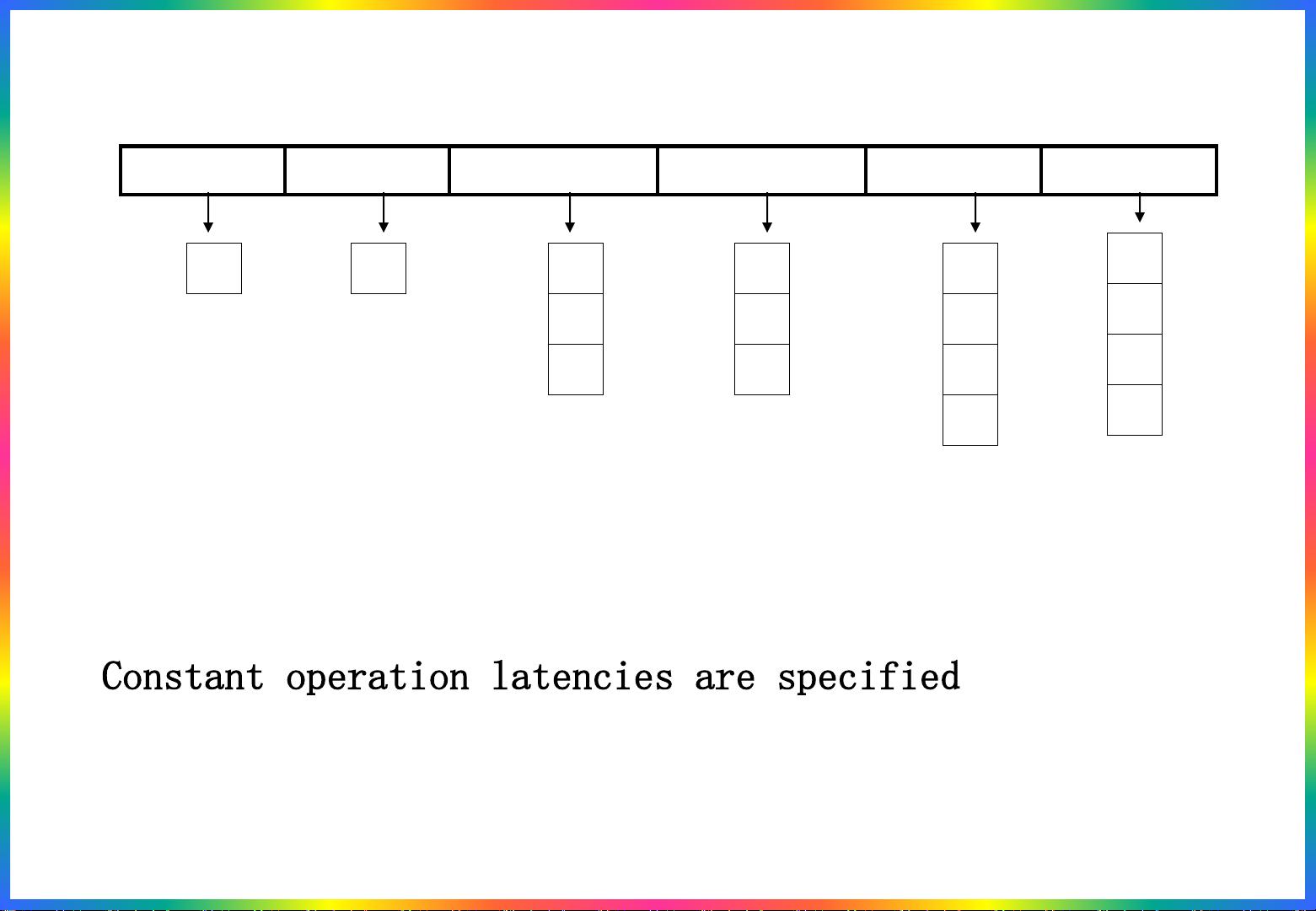

8. Control Logic Scalability:随着指令级并行度W的增加,控制逻辑的扩展变得复杂,特别是对于乱序机器,需要考虑指令缓冲器的影响以及如何维持足够的指令并行性。

9. Issue Grouping:处理器需要跟踪和管理不同组的已发出指令,这影响了整体性能。

通过这些内容,学生可以深入理解高级计算机系统结构中涉及的复杂技术,包括处理器设计的关键决策和优化策略,为未来从事高性能计算或处理器设计相关工作打下坚实基础。

2022-08-03 上传

2022-08-03 上传

2022-08-03 上传

2022-08-03 上传

2022-08-03 上传

2022-08-03 上传

2022-08-04 上传

点击了解资源详情

yiyi分析亲密关系

- 粉丝: 30

- 资源: 321

最新资源

- 天池大数据比赛:伪造人脸图像检测技术

- ADS1118数据手册中英文版合集

- Laravel 4/5包增强Eloquent模型本地化功能

- UCOSII 2.91版成功移植至STM8L平台

- 蓝色细线风格的PPT鱼骨图设计

- 基于Python的抖音舆情数据可视化分析系统

- C语言双人版游戏设计:别踩白块儿

- 创新色彩搭配的PPT鱼骨图设计展示

- SPICE公共代码库:综合资源管理

- 大气蓝灰配色PPT鱼骨图设计技巧

- 绿色风格四原因分析PPT鱼骨图设计

- 恺撒密码:古老而经典的替换加密技术解析

- C语言超市管理系统课程设计详细解析

- 深入分析:黑色因素的PPT鱼骨图应用

- 创新彩色圆点PPT鱼骨图制作与分析

- C语言课程设计:吃逗游戏源码分享