CMOS VLSI设计:SRAM简介

需积分: 11 41 浏览量

更新于2024-07-23

收藏 1.83MB PDF 举报

"这篇资料是关于VLSI设计中静态随机存取存储器(SRAM)的介绍,属于集成电路设计的基础知识。"

在计算机系统中,内存是数据存储的重要组成部分,其中静态随机存取存储器(Static Random Access Memory,简称SRAM)因其高速度和低延迟而被广泛用于缓存和高性能计算应用。SRAM是一种非易失性存储技术,它不需要持续的电源来保持数据,但相比于动态随机存取存储器(DRAM),SRAM的功耗较高且密度较低。

**CMOS VLSI Design中的SRAM**

1. **内存阵列**

内存阵列是内存设计的核心,包括随机访问内存(RAM)、串行访问内存(SAM)、内容可寻址内存(CAM)等不同类型。其中,RAM分为静态RAM(SRAM)和动态RAM(DRAM)。SRAM和DRAM的主要区别在于数据保持机制:SRAM使用静态电路结构,数据在断电后会丢失,但在供电期间不需要刷新;而DRAM则需要定期刷新以保持数据。

2. **SRAM架构**

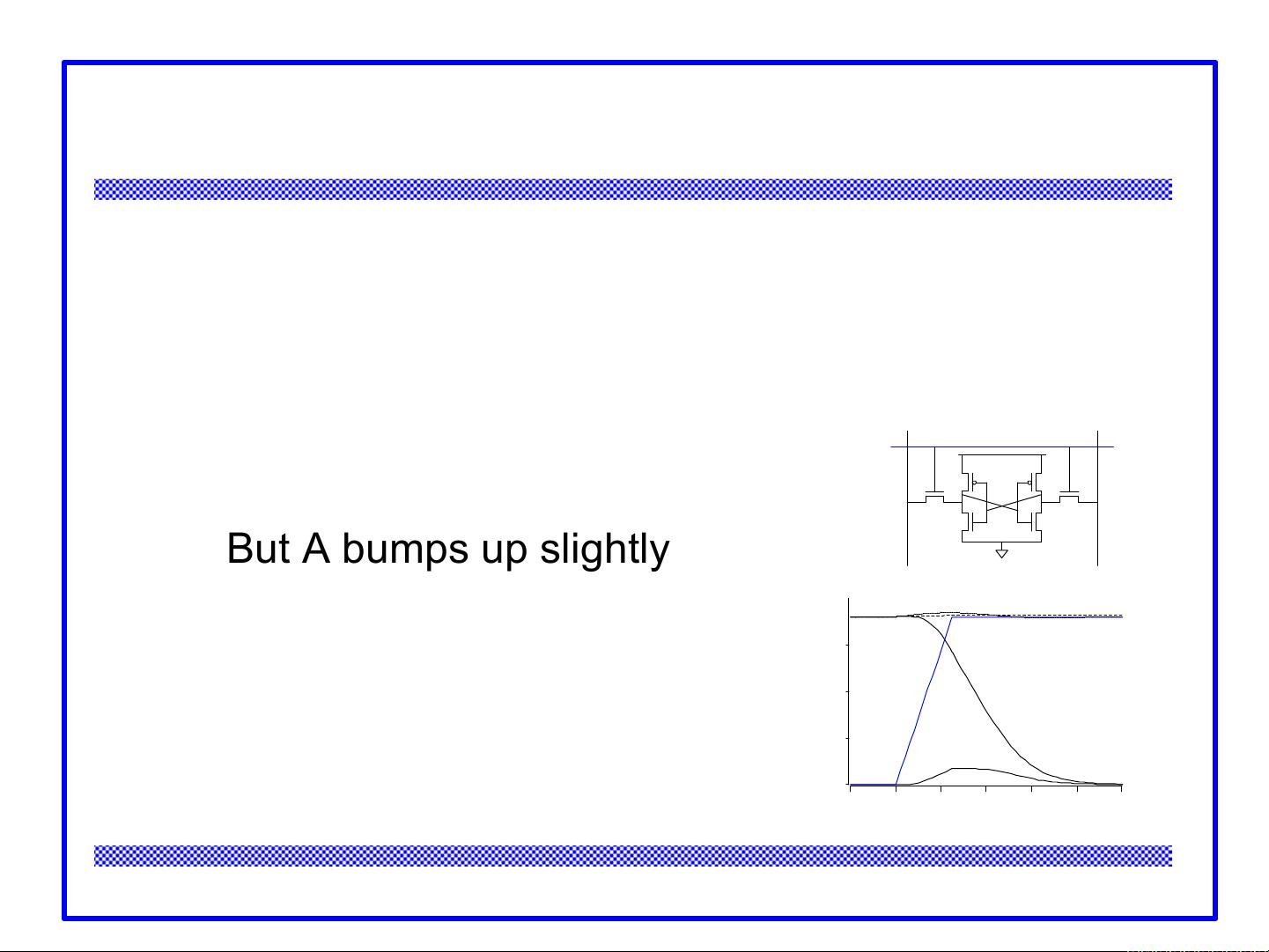

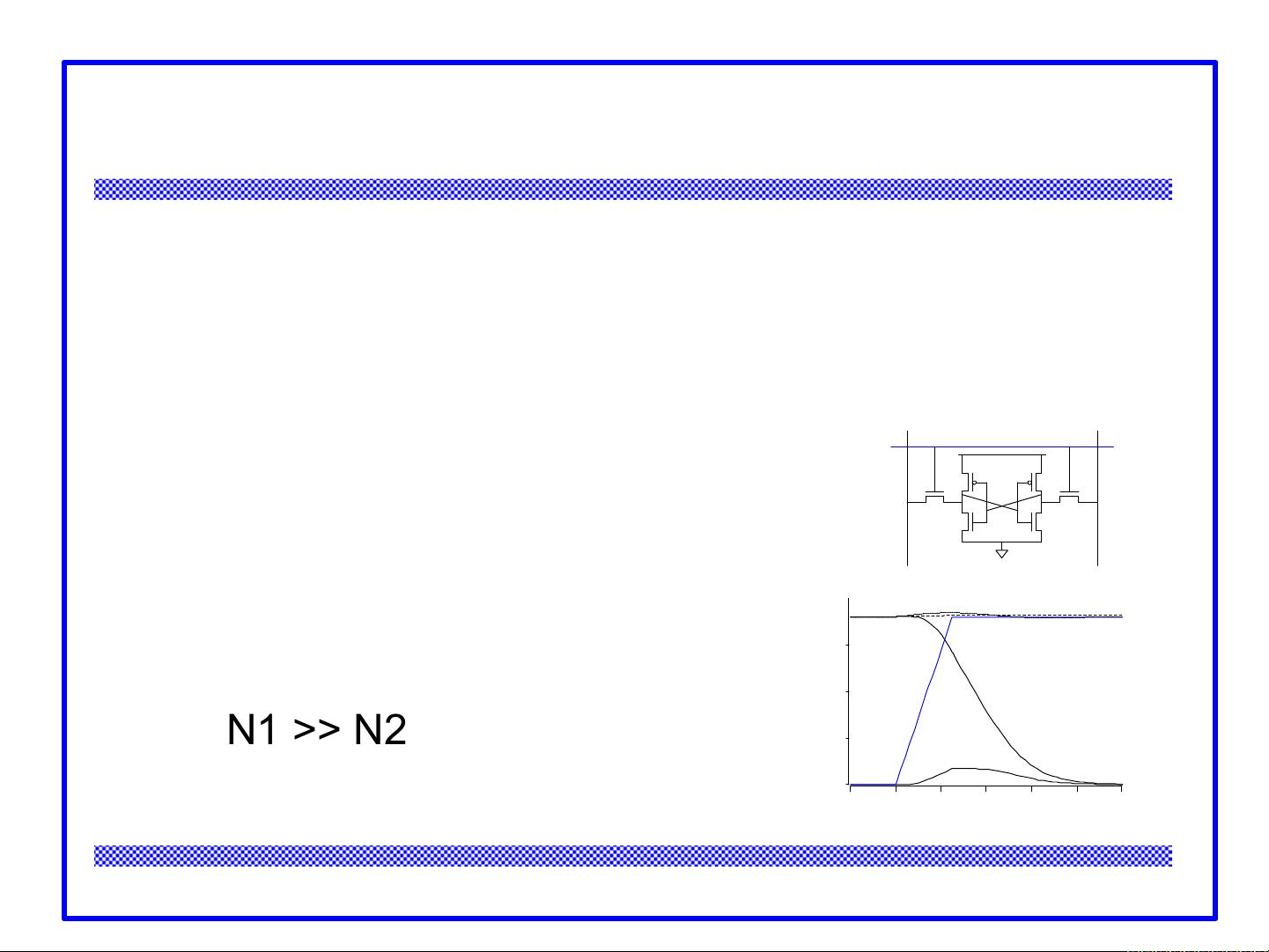

- **SRAM单元(Cell)**: SRAM的基本存储单元由六个晶体管组成,形成一个双稳态电路,可以保持两种稳定状态,代表二进制的0或1。这种电路设计使得SRAM具有较高的速度,但占用的面积较大。

- **解码器(Decoders)**: 解码器用于选择存储单元的行和列,使得我们可以对特定地址进行读写操作。

- **列电路(Column Circuitry)**: 包括位线预充电、位线选择和放大器等部分,它们负责在读取时稳定位线电压,以及在写入时将数据驱动到存储单元。

- **多端口(Multiple Ports)**: 高端的SRAM可能支持多个独立的读写端口,允许多个并发访问,提高了系统的并行处理能力。

3. **其他内存类型**

- **串行访问内存(Serial Access Memories)**: 数据按顺序读写,通常用于简单序列数据流的应用。

- **只读存储器(ROM)**: 包括掩模ROM、可编程ROM(PROM)、可擦除可编程ROM(EPROM)、电可擦除可编程ROM(EEPROM)和闪存(Flash ROM)等,这些是非易失性存储,数据在制造后无法更改或只能通过特定方式更改。

- **FIFO和LIFO**: 例如,移位寄存器、FIFO(先进先出)和LIFO(后进先出)队列,它们用于管理数据流的顺序。

**SRAM的优势与挑战**

SRAM的高速性能和即时访问能力使其成为CPU缓存的理想选择。然而,由于其结构复杂性和高功耗,SRAM通常用在需要快速存取但容量相对较小的地方,如CPU的L1和L2缓存。随着技术的发展,设计师们不断寻求优化SRAM单元设计的方法,以提高存储密度和降低功耗,同时保持其高性能特性。

总结,SRAM是VLSI设计中不可或缺的一部分,它在现代电子系统中扮演着至关重要的角色,尤其是在需要高速、低延迟数据存取的场合。理解SRAM的工作原理和技术细节对于设计高效、可靠的集成电路至关重要。

2013-05-09 上传

232 浏览量

2020-02-13 上传

105 浏览量

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情