TSMC 0.25μm CMOS工艺实现的ADC采样保持电路设计

版权申诉

DOCX格式 | 272KB |

更新于2024-09-03

| 65 浏览量 | 举报

"基于TSMC 0.25μm CMOS工艺实现ADC采样保持电路的设计"

在本文中,作者探讨了如何使用TSMC 0.25微米互补金属氧化物半导体(CMOS)工艺来设计一个高性能的模拟-数字转换器(ADC)的采样保持电路。ADC在数字信号处理中起着至关重要的作用,特别是在高速低功耗应用中,流水线结构的ADC被广泛采用。采样保持电路作为ADC的前端,对于整个系统的性能至关重要,因为它能防止采样时钟偏斜导致的信号失真。

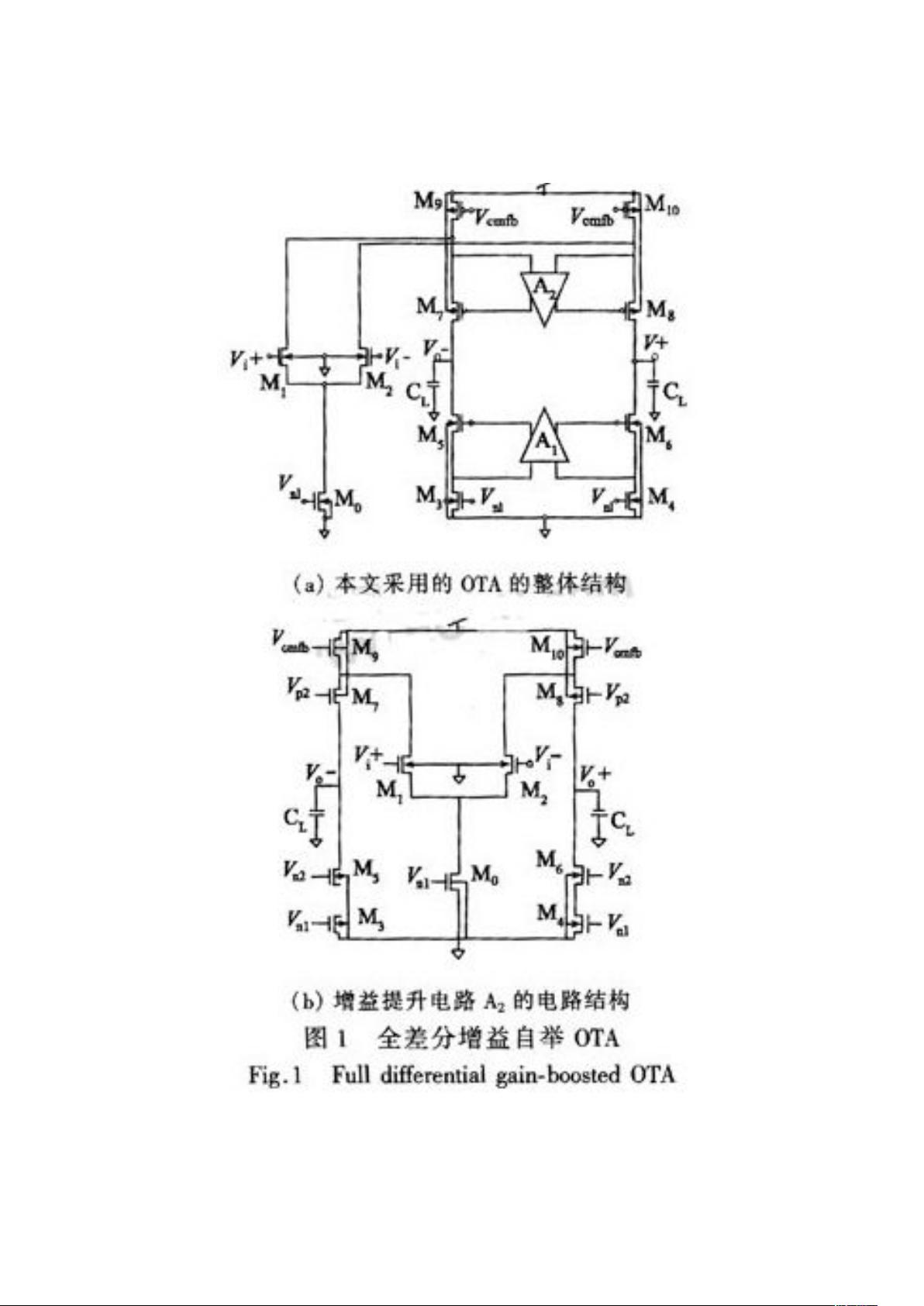

作者首先介绍了运算放大器(OTA)的设计,这是构建采样保持电路的基础。考虑到在2.5V电源电压下的工作环境,选择了折叠式共源共栅结构的OTA,因为这种结构能提供高速、高频和低功耗的特性。为了减少输入端的寄生电容并优化频率响应,使用了NMOS管作为输入管。同时,文章提到了增益自举电路的使用,以提升OTA的增益。通过这种方式,可以避免电流镜结构引入的镜像极点,从而改善OTA的频率响应。

文章进一步讨论了OTA的增益要求。在10位,100MS/s的流水线ADC中,每个阶段的有效位数(B)通常为1,这意味着OTA需要提供至少72.25dB的直流增益。为了达到这个要求,需要对OTA的各个组件进行精心设计,例如调整M7和M8管的跨导和沟道长度,以及M1和M2管的参数,以在提高增益的同时平衡寄生电容和次极点频率的影响。

采样保持电路的设计也是文章的重点。采样保持电路的任务是在ADC的采样阶段保持输入信号的值,确保在转换期间信号不发生变化。设计时需要考虑的关键参数包括采样速度、保持时间、输入阻抗和输出噪声等。作者可能详细讨论了这些参数的选择和优化方法,以及如何通过OTA来实现这一功能,但具体内容未在提供的摘要中详述。

此外,文章还可能涵盖了电路的仿真结果和性能分析,这包括但不限于噪声性能、增益误差、带宽限制以及功耗等方面的评估。通过这些仿真数据,可以验证设计是否满足预期的ADC性能指标。

这篇文档详细阐述了基于TSMC 0.25μm CMOS工艺的ADC采样保持电路设计的各个方面,从OTA的选择和优化到采样保持电路的实现,都是为了在高速、低功耗的环境下提供高质量的模拟-数字转换性能。这样的设计对于现代电子设备,尤其是那些依赖于精确数字信号处理的设备来说,具有很高的实用价值。

相关推荐

ziyoudianzi15

- 粉丝: 0

最新资源

- 自动生成CAD模型文件的测试流程

- 掌握JavaScript中的while循环语句

- 宜科高分辨率编码器产品手册解析

- 探索3CDaemon:FTP与TFTP的高效传输解决方案

- 高效文件对比系统:快速定位文件差异

- JavaScript密码生成器的设计与实现

- 比特彗星1.45稳定版发布:低资源占用的BT下载工具

- OpenGL光源与材质实现教程

- Tablesorter 2.0:增强表格用户体验的分页与内容筛选插件

- 设计开发者的色值图谱指南

- UYA-Grupo_8研讨会:在DCU上的培训

- 新唐NUC100芯片下载程序源代码发布

- 厂家惠新版QQ空间访客提取器v1.5发布:轻松获取访客数据

- 《Windows核心编程(第五版)》配套源码解析

- RAIDReconstructor:阵列重组与数据恢复专家

- Amargos项目网站构建与开发指南