Calibre后仿真教程:CADENCE使用与版图验证解析

"这篇教程详细介绍了如何使用calibre进行CADENCE后仿真,主要针对微电子领域的版图设计和验证。作者马彦昭来自西安交通大学微电子研究所,教程内容包括工作环境设置、版图设计和版图验证等关键步骤。"

在微电子设计中,CADENCE与calibre的组合是进行后仿真和验证的重要工具。calibre是一款业界广泛使用的版图验证软件,能够对设计规则检查(DRC)、电气规则检查(ERC)、布局与原理图对比(LVS)等多个方面进行全面验证。

首先,要正确配置工作环境。在用户环境变量`.cshrc`文件中,设置`MGC_DOC_PATH`指向`Calibre_HOME/docs/`,以便访问calibre的帮助文档。同时,在CADENCE的初始化文件`.cdsinit`中加载calibre的技能文件,这样可以在CADENCE环境中直接调用calibre。

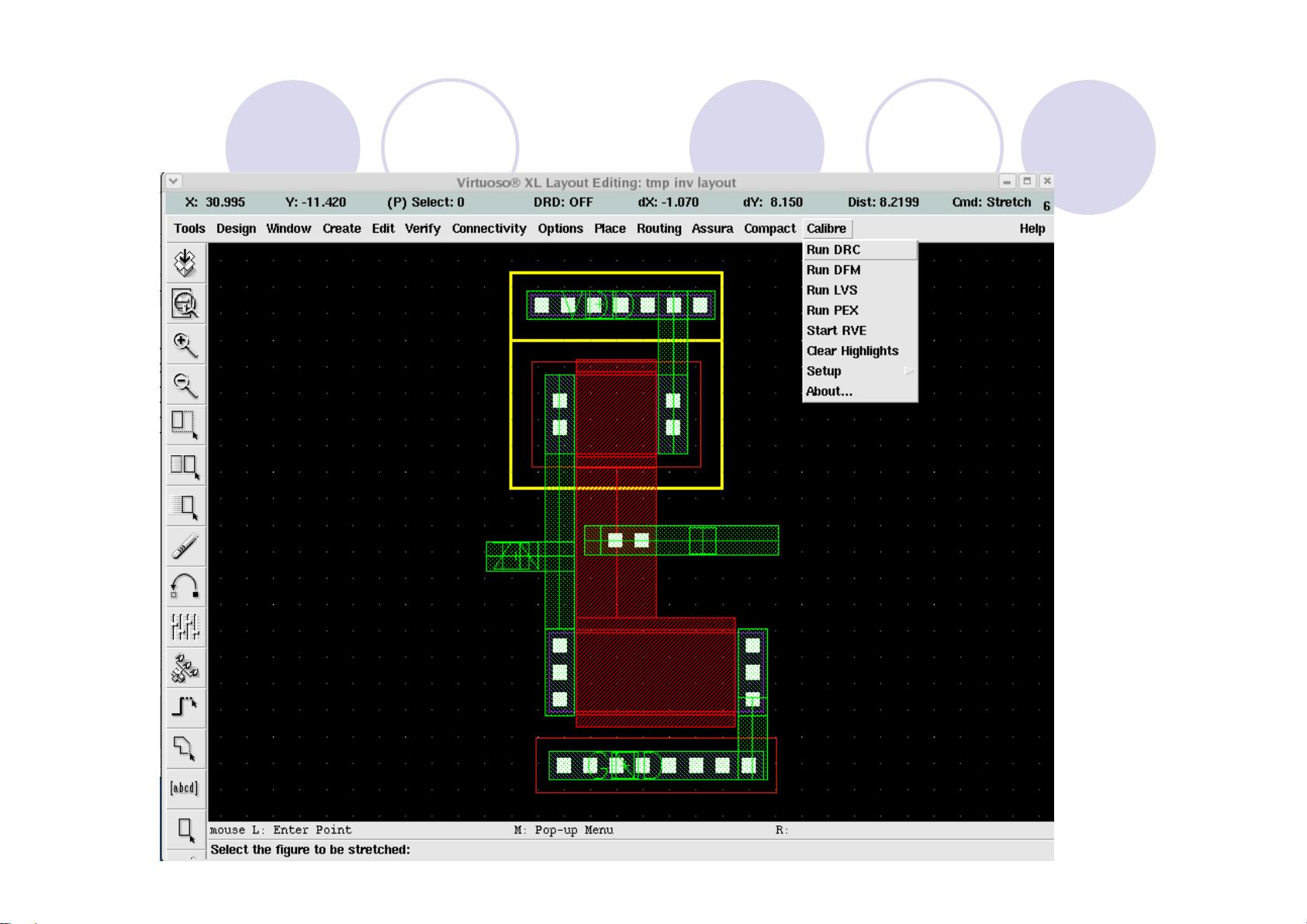

接着,通过运行`layoutver.sh`脚本来建立工作环境。进入版图设计目录,启动CADENCE并开始绘制版图。在CADENCE中,可以通过Tools -> DesignSynthesis -> LayoutXL打开电路图,然后使用Design -> GenFromSource…创建版图文件,并取消Boundary选项,以便自定义版图边界。对于输入/输出引脚,选择相应的层,并通过PinLabelOptions设置标识层。在设计过程中,黄线会显示节点间的连接状态,帮助完成版图的其他部分。

在版图设计完成后,需要进行验证以确保设计符合规则和电气要求。主要的验证步骤包括:

1. **DRC (Design Rule Checking)**:检查版图是否违反了设计规则。通过指定LAYOUTPATH、LAYOUTPRIMARY、layoutsystemGDS2和DRCRESULTSDATABASE等参数,设置DRC规则并执行检查,结果将保存在DRCSUMMARYREPORT中。

2. **ERC (Electrical Rule Checking)**:检查电气规则,如短路、开路等问题。

3. **LVS (Layout Versus Schematic)**:对比版图和原理图,确保两者的一致性。

4. **PEX (Post-layout Extraction)**:版图提取,分析版图的电学特性。

5. **RVE (Results Viewing Environment)**:用于查看和分析验证结果的环境窗口。

6. **SVDB (Standard Verification Database)**:存储LVS的结果,供后续分析使用。

通过这些步骤,工程师可以确保微电子设计的准确性和合规性,降低制造过程中的风险。对于初学者来说,这个教程提供了一个逐步指导的过程,使得CADENCE和calibre的使用不再那么困难。

相关推荐

vzhenyi

- 粉丝: 24

最新资源

- C++实现的注册表锁定与解锁函数

- IDL编程入门与实践:数据可视化分析

- 李建忠与侯捷:面向对象设计与应对复杂性的策略

- C++编写的多宿舍局域网聊天信使源码

- C++ U盘程序源码:基础文件传输与字符串操作

- Linux命令全览:cat、cd与chmod详解

- Sniffer中文教程:网络协议分析与故障解决

- Windows文件属性操作详解:包括隐藏、只读等设置

- C语言在嵌入式系统中的应用与挑战

- Web浏览器历史与AJAX基础

- SQL Server 设计与编码规范详解

- C#新版设计模式详解:从单例到访问者模式

- IAR EWARM入门教程:轻松开发ARM7应用

- Oracle函数参考指南

- Java编程入门:理解变量与类型

- 思科网络工程师认证实战指南