FPGA设计时钟因素分析:确保系统稳定性的关键

需积分: 9 5 浏览量

更新于2024-10-15

收藏 311KB PDF 举报

"本文主要探讨了影响FPGA设计中时钟因素的重要性,特别是建立时间和保持时间的概念,并通过分析同步设计模型来阐述如何确保时序逻辑的稳定性。"

在FPGA设计中,时钟起着至关重要的作用,因为它控制着系统内大部分器件的操作。时钟的精度和一致性直接影响着系统的性能和稳定性。时钟信号的时延差应尽可能小,以避免导致时序逻辑错误。因此,理解并优化决定系统时钟的因素是FPGA设计的关键。

1、建立时间和保持时间

建立时间(Tsu)是指数据在时钟上升沿到来前必须稳定的时间,而保持时间(Th)是指数据在时钟上升沿后需要保持稳定的时间。这两个参数是确保数据正确被触发器捕获的必要条件。如果建立时间不足,数据可能无法稳定地进入触发器;同样,如果保持时间过短,数据也可能无法被正确捕获。在FPGA设计中,理解并计算这些时间至关重要,特别是在组合逻辑和时序逻辑的接口处。

2、同步设计模型分析

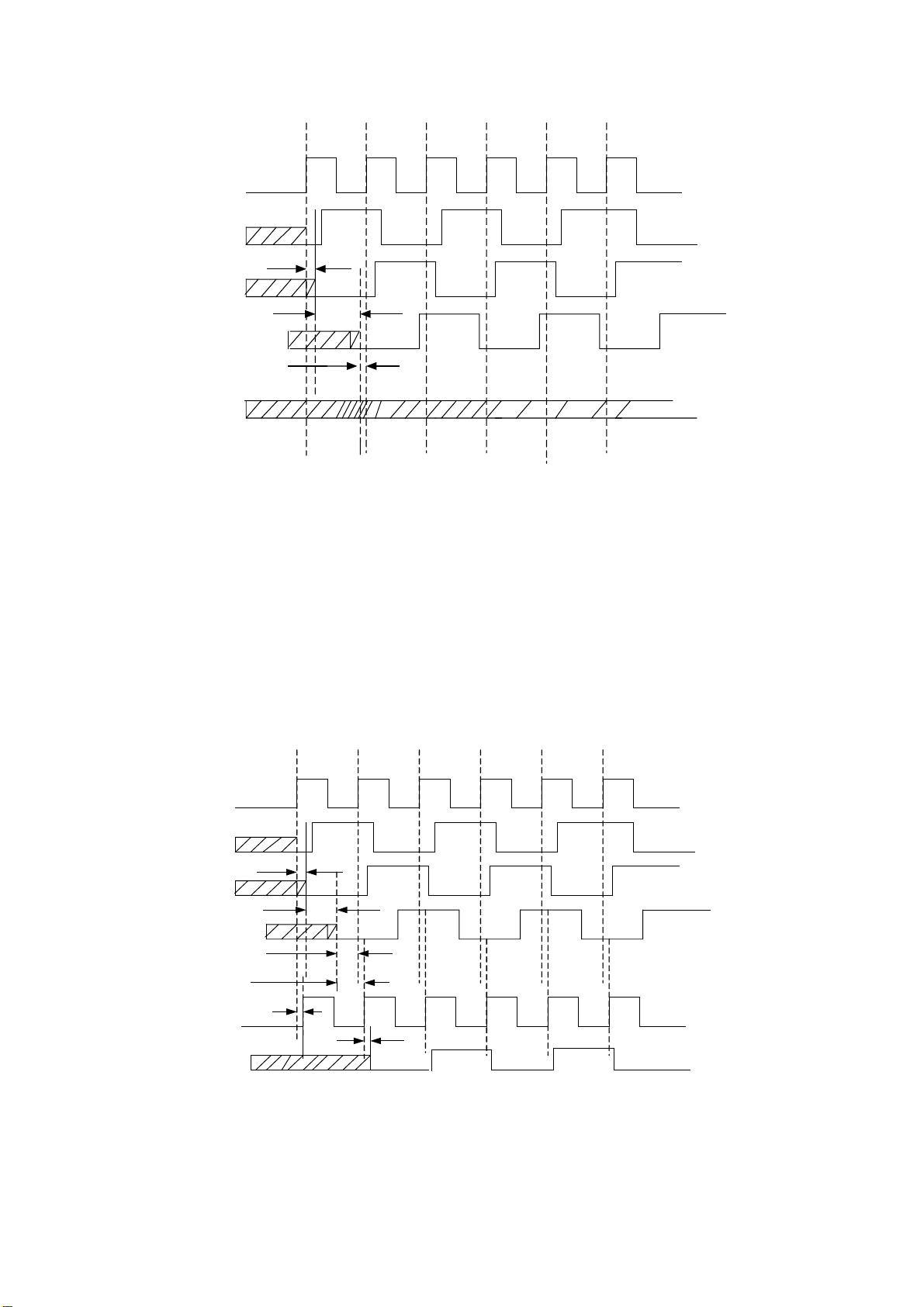

图2展示了一个典型的同步设计模型,其中所有组件共享同一时钟。Tco表示触发器的输出延迟,Tdelay表示组合逻辑延迟,Tsetup是触发器的建立时间,Tpd是时钟延迟。设计者需要确保在最大和最小延迟边界内,第二个触发器D2的建立时间T3和保持时间T4满足要求。如果时钟延迟Tpd可以忽略(如在FPGA设计中常见的全局时钟网络),那么保持时间通常不成问题,但建立时间的计算则更为关键。

在分析时序图时,我们通常考虑两种情况:一是假设时钟延迟为零,此时关注点在于确保建立时间满足要求;二是考虑非零时钟延迟,这时需要同时考虑建立时间和保持时间,以确保在任何条件下数据都能正确传输。

3、优化时钟路径

为了确保设计的稳定性,设计师需要关注以下几个方面:

- **减少时钟树的延迟**:通过优化布线和使用低延迟时钟缓冲器可以减少Tpd,从而降低建立时间的风险。

- **均衡时钟网络**:确保所有时钟信号到达各个部分的时间尽量一致,减少时钟 skew,这对于高速设计尤为重要。

- **使用时序分析工具**:这些工具可以帮助识别和解决潜在的时序问题,如建立时间违反或保持时间违反。

- **时钟门控**:根据需要动态关闭某些部分的时钟,可以减少功耗并提高设计的灵活性。

4、约束驱动设计

在实现FPGA设计时,必须定义和应用适当的时序约束,以指导合成工具进行优化。这些约束包括时钟周期、建立时间和保持时间限制,它们有助于确保设计在不同工作条件下的可靠性。

理解并优化FPGA设计中的时钟因素对于创建高效、可靠的系统至关重要。这涉及对建立时间、保持时间的深入理解和对同步设计模型的分析,以及通过优化时钟路径、使用时序分析工具和设定适当约束来确保设计的时序完整性。

2020-08-07 上传

2010-10-01 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-04-27 上传

2010-08-20 上传

2012-02-25 上传

leter15

- 粉丝: 0

- 资源: 2

最新资源

- Condition-monitoring-of-hydraulic-systems-using-xgboost-modeling:我们将使用各种传感器值并使用xgboost进行测试液压钻机的状态监控

- 齐尔奇

- cubelounge:基于立方体引擎的游戏社区网站

- csharp_s7server_snap7_snap7c#代码_C#S7协议_c#s7连接plc_c#s71500

- Excel模板基础体温记录表格.zip

- lab_prog_III

- lekce03-priklad01:第3课示例

- ember-cli-htmlbars

- Recommendation-System:基于相似性创建简单的推荐系统

- React Native 的可扩展组件

- Excel模板简易送货单EXCEL打印模板.zip

- DependencyWalker:PE格式图像依赖解析器

- 数据结构基础系列(6):树和二叉树

- neuro-network-visualizer-web-app-python:使用Streamlit的神经网络Visualizer Web应用程序,以及使用Keras和Flask的简单模型服务器

- SentimentAnalysis

- mayorleaguec23:Basi HTML页面