FPGA设计:时钟因素与系统稳定性的关键分析

192 浏览量

更新于2024-08-31

收藏 573KB PDF 举报

"本文深入探讨了影响FPGA设计中时钟因素的重要性,强调了时钟信号时延差小对于保证系统稳定性的关键作用,并详细解释了建立时间和保持时间的概念及其在设计中的应用。"

在FPGA(Field-Programmable Gate Array)设计中,时钟的准确性和一致性至关重要,因为它驱动着系统内大部分器件的操作。时钟信号的时延差如果过大,可能导致时序逻辑错误,从而破坏整个电路的功能。因此,理解并控制这些时序参数对于确保设计的可靠性是至关重要的。

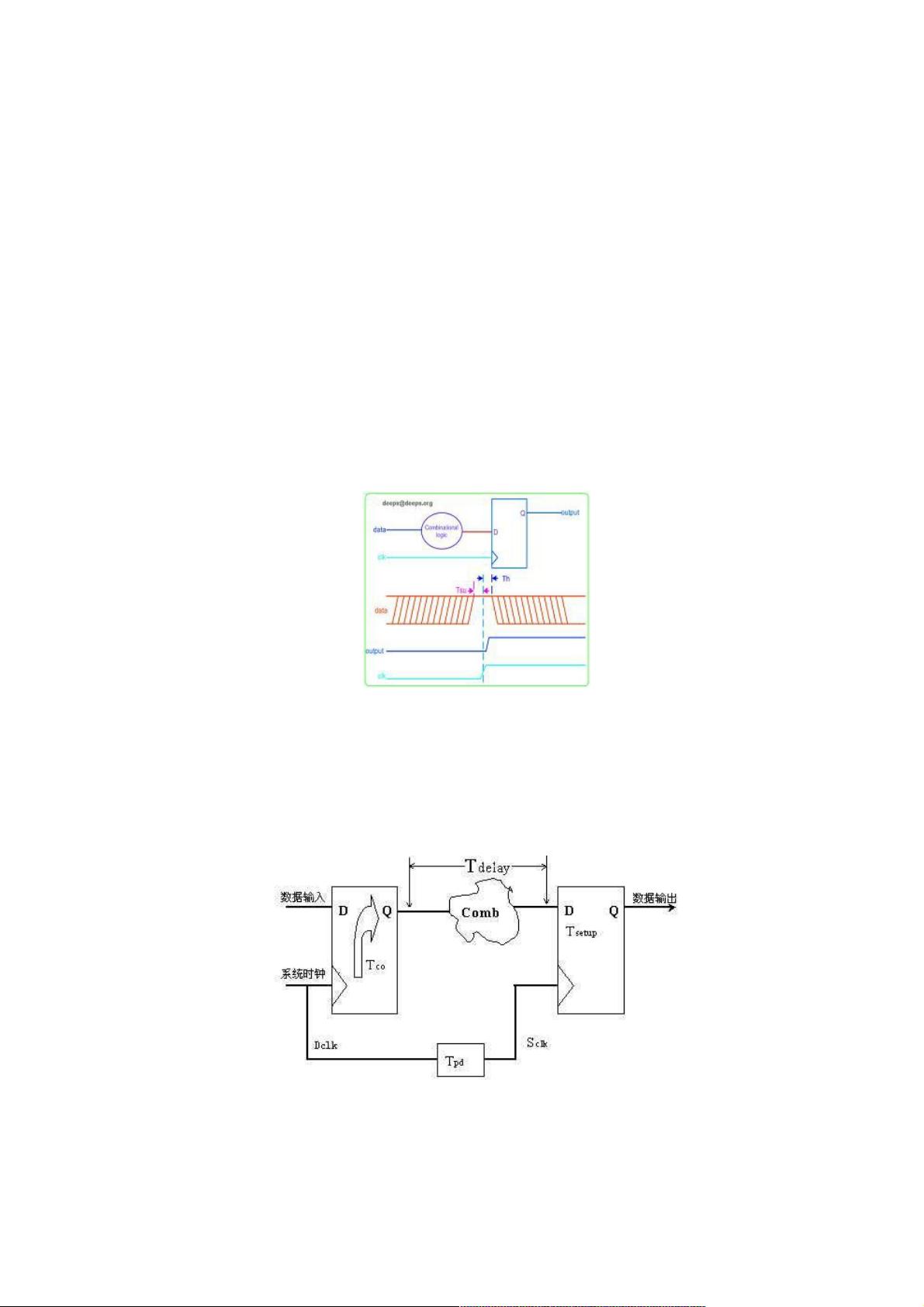

时序参数主要包括建立时间和保持时间。建立时间(Tsu)定义为数据需要在时钟上升沿到来前稳定的时间,以确保触发器能够正确捕获数据。如果数据未能在规定时间内稳定,可能会导致触发器无法正确工作。而保持时间(Th)是指数据在时钟边沿之后需要保持稳定的时间,以避免在下一个时钟周期内出现错误。这两者是保证时序正确性的基本条件。

在FPGA设计中,通常会使用统一的时钟源,这使得内部时钟延时可以忽略不计。在这种情况下,主要关注的是建立时间,因为数据的延迟通常远大于时钟延迟,因此保持时间通常不会成为问题。图3展示了当时钟延时为零时,如果D2的建立时间满足条件,理想的时序图。在这种理想情况下,只要确保数据在时钟上升沿到来前足够稳定,就能保证正确传输。

然而,实际情况中,时钟会有一定的传播延迟(Tpd),这可能会影响建立时间和保持时间的计算。例如,如果时钟有非零延迟,那么在设计时需要考虑到这个延迟对整个时序路径的影响。图2中的模型描绘了这种复杂情况,其中T1max和T1min分别代表第一个触发器的建立时间范围,T2max和T2min表示组合逻辑的延时范围。要确保第二个触发器D2的时序正确,需要计算D2的建立时间T3和保持时间T4应满足的条件,或者反过来,根据已知的T3和T4确定允许的最大时钟周期。

在实际设计中,这通常涉及到复杂的时序分析和优化,包括但不限于使用仿真工具检查所有可能的路径,调整逻辑布局,减小组合逻辑的延时,以及选择合适的时钟分频器或PLL(Phase-Locked Loop)来减少时钟的延迟。同时,还需要考虑到温度、电压波动等因素对时钟和逻辑延迟的影响,确保设计在各种工作条件下都能保持时序合规。

FPGA设计中的时钟管理是一个精细且至关重要的任务,它需要深入理解时序约束,并结合适当的工具和技术进行精确的计算和优化。通过充分掌握建立时间、保持时间等概念,设计师可以有效地防止时序错误,从而创建出高效、可靠的FPGA设计方案。

2012-03-09 上传

2010-10-01 上传

点击了解资源详情

2021-04-27 上传

2010-08-20 上传

2012-02-25 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

weixin_38693720

- 粉丝: 10

- 资源: 900

最新资源

- iamjoshbraun博客

- Password-Management-System-Nodejs-Mini_Project:使用Node js,Express js和Mongoose的初学者密码管理系统迷你项目

- reactjs-starter-kit:用于webpack捆绑包上的React JS应用的入门工具包(带有SCSS模块)

- SCA_SCA优化算法_正弦余弦优化算法_SCA_优化算法_正弦余弦算法

- Excel模板居民消费价格指数分析统计.zip

- algorithms-text-answers:在算法入门第3版中跟踪我的进度

- node-craigslist:搜索Craigslist.com列表的节点驱动程序

- physics_based_learning:计算成像系统的学习变得简单

- Python库 | python-google-places-1.2.0.tar.gz

- PMSM-vector-control_pmsm_BLDC_foc_滑膜观测器

- Ox_covid_data_and_charts

- react-native-smaato:Smaato支持** Android **和** iOS **

- Memoria-fox:用javascript编写的简单记忆游戏

- Python-Projects

- COMP397-KIIONICS-隐藏

- foundations_course:自治系统硕士课程新生的预备课程材料