FPGA设计时钟因素分析:建立时间与保持时间的重要性

需积分: 1 155 浏览量

更新于2024-09-15

收藏 284KB PDF 举报

"本文主要探讨了影响FPGA设计中时钟因素的重要性,特别是建立时间和保持时间的概念,并通过一个同步设计的基本模型分析了如何确保时序逻辑的稳定性。"

在FPGA设计中,时钟是系统运行的核心,因为它控制着所有数字逻辑的操作。时钟信号的精度和一致性对整个系统的性能和可靠性至关重要。文中提到了两个关键概念:建立时间和保持时间。

建立时间(Tsu)是指数据必须在时钟边沿到来前稳定的时间,以确保触发器能在下一个时钟周期正确捕获数据。如果数据在时钟上升沿到来前未达到稳定,可能会导致触发器无法正确采样,从而引发错误。保持时间(Th)则是在时钟边沿之后数据必须保持稳定的时间,以确保在时钟周期内数据不会改变,否则同样可能导致触发器读取错误的数据。

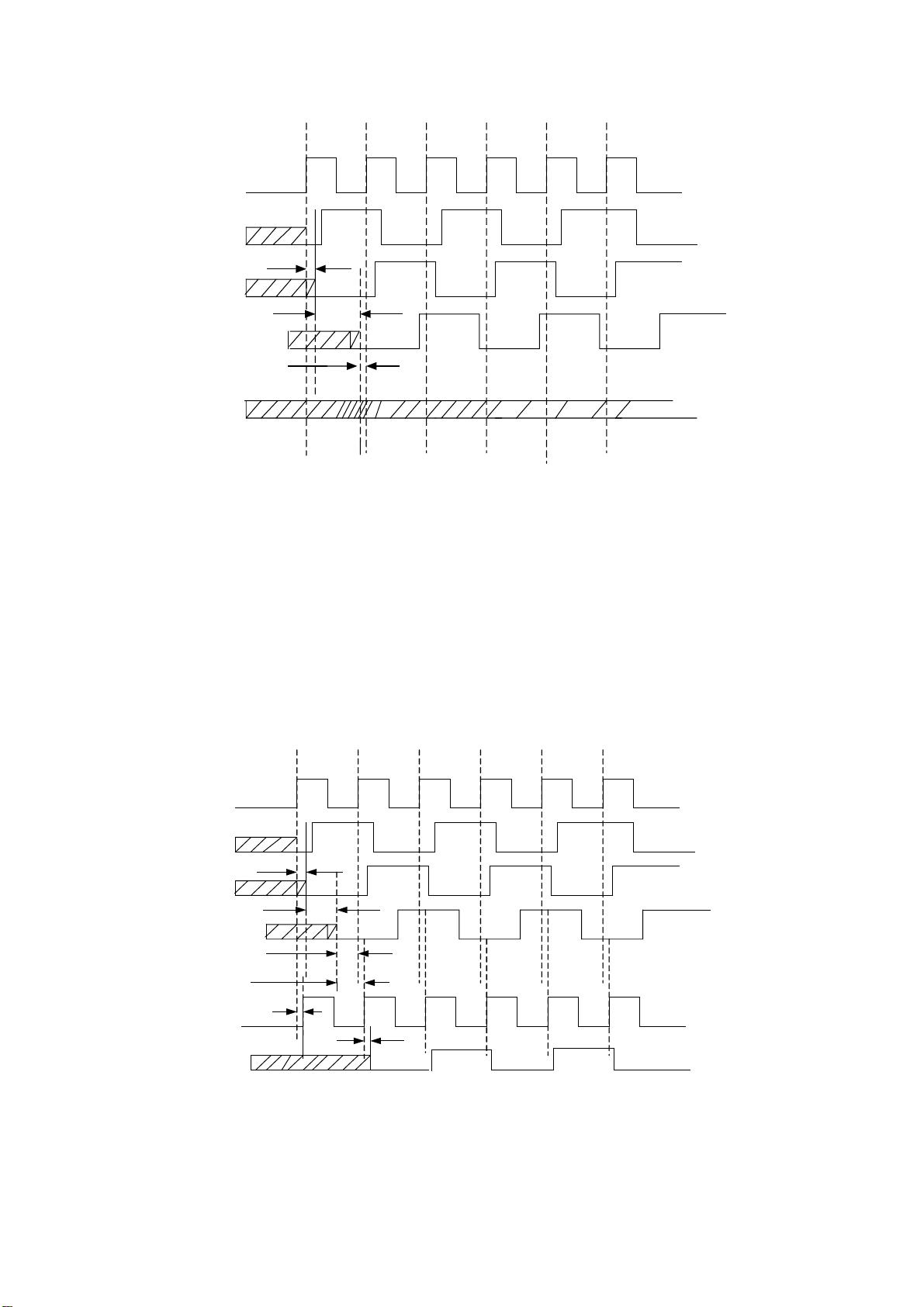

图2展示了一个同步设计模型,其中包含了组合逻辑和时序逻辑。Tco表示触发器的输出延迟,Tdelay表示组合逻辑的延迟,Tsetup是触发器的建立时间,而Tpd是时钟的延迟。设计中必须确保在各种可能的延时条件下,D1和D2之间的路径满足建立时间和保持时间的要求。例如,如果D1的建立时间范围是T1min到T1max,组合逻辑的延迟范围是T2min到T2max,那么需要计算出D2的建立时间T3和保持时间T4的合适范围,以确保整个设计的时序正确性。

在FPGA设计中,通常使用全局时钟,其内部延时可以忽略不计,这使得保持时间通常不成问题。然而,建立时间仍然是设计的关键,因为它决定了数据能否在时钟边沿到来前稳定。因此,设计者需要精确地计算和优化各个路径的延迟,确保所有数据路径都能在时钟的建立时间内稳定。

在实际的设计过程中,还需要考虑其他因素,如时钟抖动、时钟网络的扇出、工艺、电压和温度(PVT条件)的影响,以及电源噪声等。时钟树的布局布线、时钟分配网络的均衡性和时钟域间的同步问题也是FPGA设计中不可忽视的部分。此外,时钟管理技术,如锁相环(PLL)、分频器和时钟缓冲器(DLL),都是用来优化时钟质量和同步性的关键工具。

理解并掌握时钟因素对于FPGA设计至关重要,它直接影响到系统的性能、功耗和可靠性。在设计阶段,设计师需要通过深入理解建立时间和保持时间,以及它们与组合逻辑和时序逻辑的关系,来确保设计的时序正确性,从而构建高效且可靠的FPGA系统。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2020-08-07 上传

2010-10-01 上传

点击了解资源详情

2013-10-07 上传

2010-08-20 上传

2012-02-25 上传

corton

- 粉丝: 0

- 资源: 1

最新资源

- reek:Ruby的代码气味检测器

- c代码-打印长方形

- learnersourcing-subgoal-labels:学习视频的学习者外包工作流程

- 一般管理学原理概述.zip

- auto-store-proCode-

- react-component-octicons:Octicons的零依赖React组件

- 之江杯train-数据集

- PHP-Rocks:PHP Rocks,一个现代,无脂肪且易于使用的框架。 100%单元测试覆盖率,带有travis的CI

- music-lib-bot:因为我懒得拖放

- 虾:快速,灵活的Ruby PDF编写器

- weather-console-app:Node.js中的简单天气应用程序

- foss-spring-2021-hackmd-notes:使用hackmd试用笔记

- gulp-deploy-git:自动将Gulp构建部署到Git存储库

- mail:使用Python和React构建的邮件应用程序

- 精美水墨古典风国学文化PPT模板

- ImageSimilarityComparison:查找两个图像之间的相似性