集成电路设计与验证:基于单元的实现方法

"Cell-based IC Design and Verification"

在IC设计领域,Cell-based IC Design and Verification 是一种常见的方法,它涵盖了从概念到物理实现的整个设计流程。这个过程包括了多个关键步骤,确保集成电路(IC)的高效、可靠和功能完备。

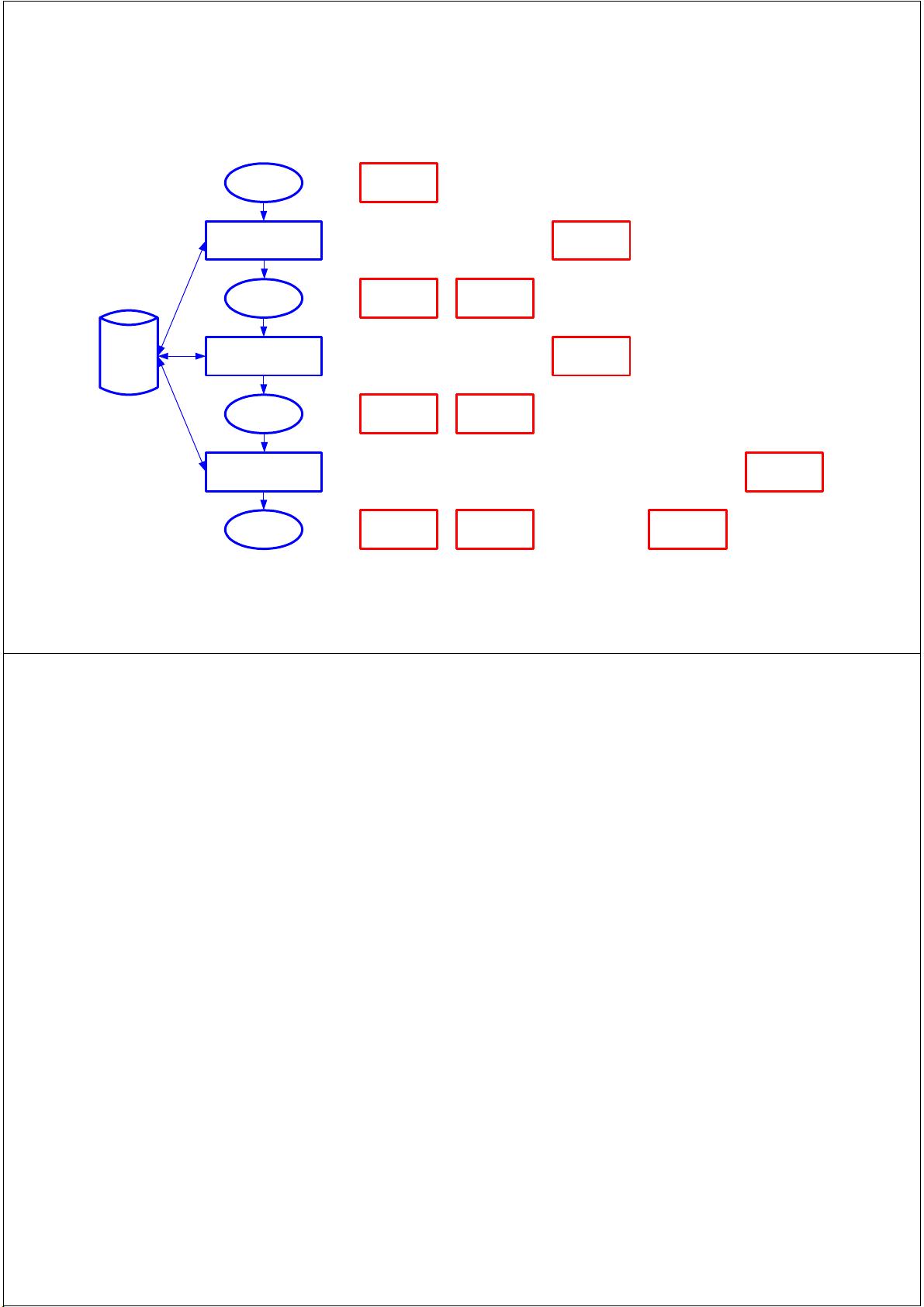

1. **Design Flow Overview**:设计流程概述是整个过程的起点,定义了从算法到芯片实现的各个阶段。通常,这包括需求分析、系统级设计、RTL(寄存器传输级)编码、仿真验证、逻辑综合、时序分析、布局布线、物理验证以及最终的测试和验证。

2. **Verilog at a Glance**:Verilog是一种硬件描述语言(HDL),用于描述数字系统的结构和行为。它是RTL设计的核心,允许设计师以抽象的方式表达电路逻辑。

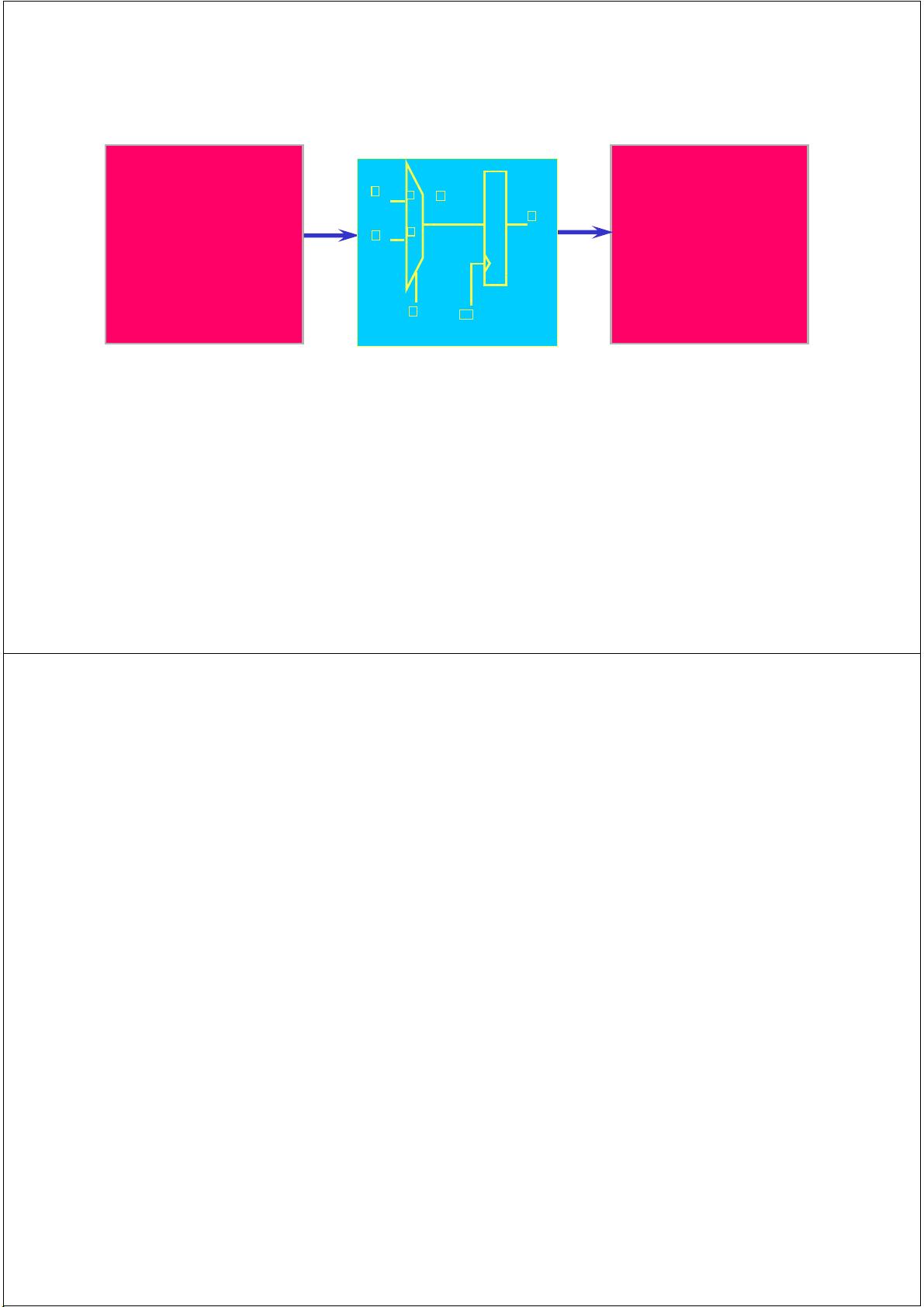

3. **RTL Simulation**:RTL仿真在设计流程中用于验证设计的功能正确性。通过输入测试向量并观察预期的输出,确保设计满足规格要求。

4. **Code Coverage Analysis**:代码覆盖率分析用于评估测试用例对设计覆盖的程度,确保所有可能的代码路径都得到了测试。

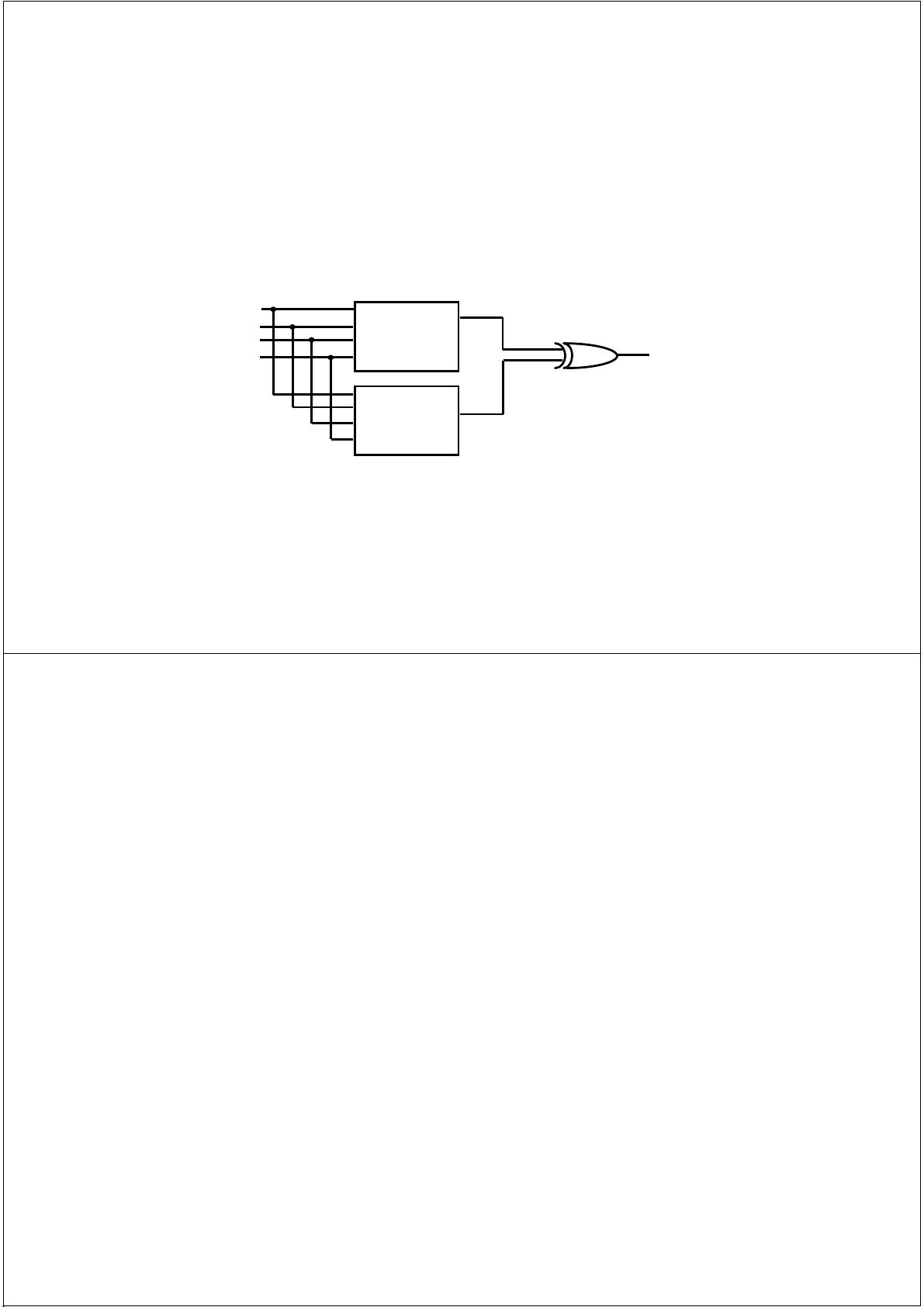

5. **RTL Synthesis**:此步骤将RTL代码转换为门级网表,优化逻辑以提高性能和面积效率。

6. **Logic Synthesis**:逻辑综合进一步优化门级网络,可能涉及逻辑等效替换、门级优化等,以达到设计的时序和面积目标。

7. **Gate-level Delay Calculation**:计算门级延迟是评估电路运行速度的关键,它涉及到信号在门之间传递的时间。

8. **Static Timing Analysis (STA)**:静态时序分析用于确定电路在最坏情况下的运行时间,以确保满足时序约束。

9. **Power Analysis & Optimization**:电源分析和优化关注电路的功耗,通过各种技术减少静态和动态功耗,如低功耗设计策略、电压岛划分等。

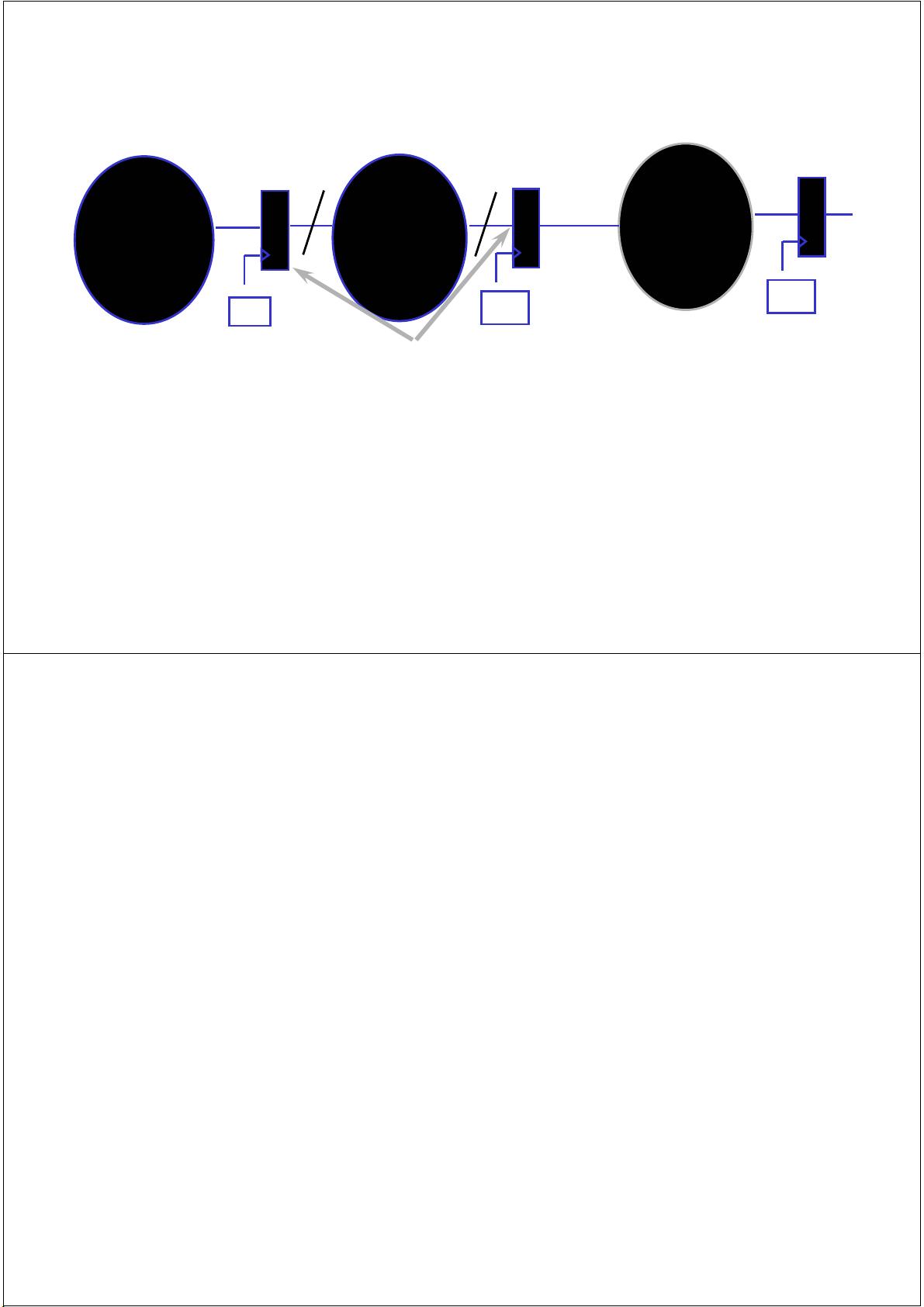

10. **DFT (Design for Testability) & ATPG (Automatic Test Pattern Generation)**:DFT是为了方便测试而设计电路,ATPG则生成测试向量,确保能检测出设计中的所有故障。

11. **Automatic Physical Design**:自动物理设计使用自动化工具进行布局和布线,以满足时序、功耗和面积目标。

12. **Physical Verification**:物理验证确保设计符合工艺规则,无结构冲突,并满足电气规则。

13. **Formal Equivalence Checking**:形式等价检查验证经过综合和布局布线后的门级设计是否与原始的RTL设计等价,确保功能一致性。

整个设计流程是一个迭代过程,每个步骤都可能需要返回上一步进行修改和优化,直到满足所有规格和性能指标。黄俊铭的讲座详细介绍了这些步骤,提供了实践实验室环节,帮助学习者掌握相关工具的使用,如Verilog-XL、VNCover、Design Compiler、PowerCompiler、DFTCompiler、Apollo 和 Conformal LEC,这些都是IC设计和验证过程中不可或缺的工具。

2019-05-23 上传

2023-12-31 上传

134 浏览量

点击了解资源详情

点击了解资源详情

点击了解资源详情

dominer

- 粉丝: 0

- 资源: 1

最新资源

- AJAX开发简略.pdf

- PowerBuilder8.0中文参考手册.pdf

- struts2.0+hibernate3.1+spring2.0的使用.doc

- VB中与串口通讯需要用到的控件介绍

- cpu卡基础知识与入门方法

- c++ TR1 文档

- 虚拟键盘的驱动程序 制作虚拟键盘的过程和

- MRPII-最经典的教材

- GRAILS中文开发PDF文档

- c++ 小游戏 程序

- 深入浅出Struts2.pdf

- 网络工程师英词典 网工英语词汇表.pdf

- Ubuntu实用学习教程

- Linux.C++.Programming.HOWTO

- QTP初级使用手册QTP8_Tutorial_oldsidney_cn

- 注册表概述精华及普遍误区