VHDL设计:可校时分秒定时器电路

需积分: 27 195 浏览量

更新于2024-09-17

1

收藏 138KB DOC 举报

"本文主要介绍了使用VHDL设计的时分秒可校的定时器电路,包括系统的总体设计、单元电路设计、软件设计、系统测试、结论和参考文献。设计中,定时器由59进制和24进制的减计数器组成,能够显示并报警定时结束。此外,还提供了倒计时电路(以秒为例)的详细描述,以及七段数码管显示的原理。"

在电子设计领域,VHDL(Very High Speed Integrated Circuit Hardware Description Language)是一种重要的硬件描述语言,常用于数字逻辑系统的设计,如FPGA(Field-Programmable Gate Array)和ASIC(Application-Specific Integrated Circuit)等。在这个定时器设计中,VHDL被用来描述和实现各种功能模块,包括定时模块、显示模块和报警模块。

1. **系统设计**:

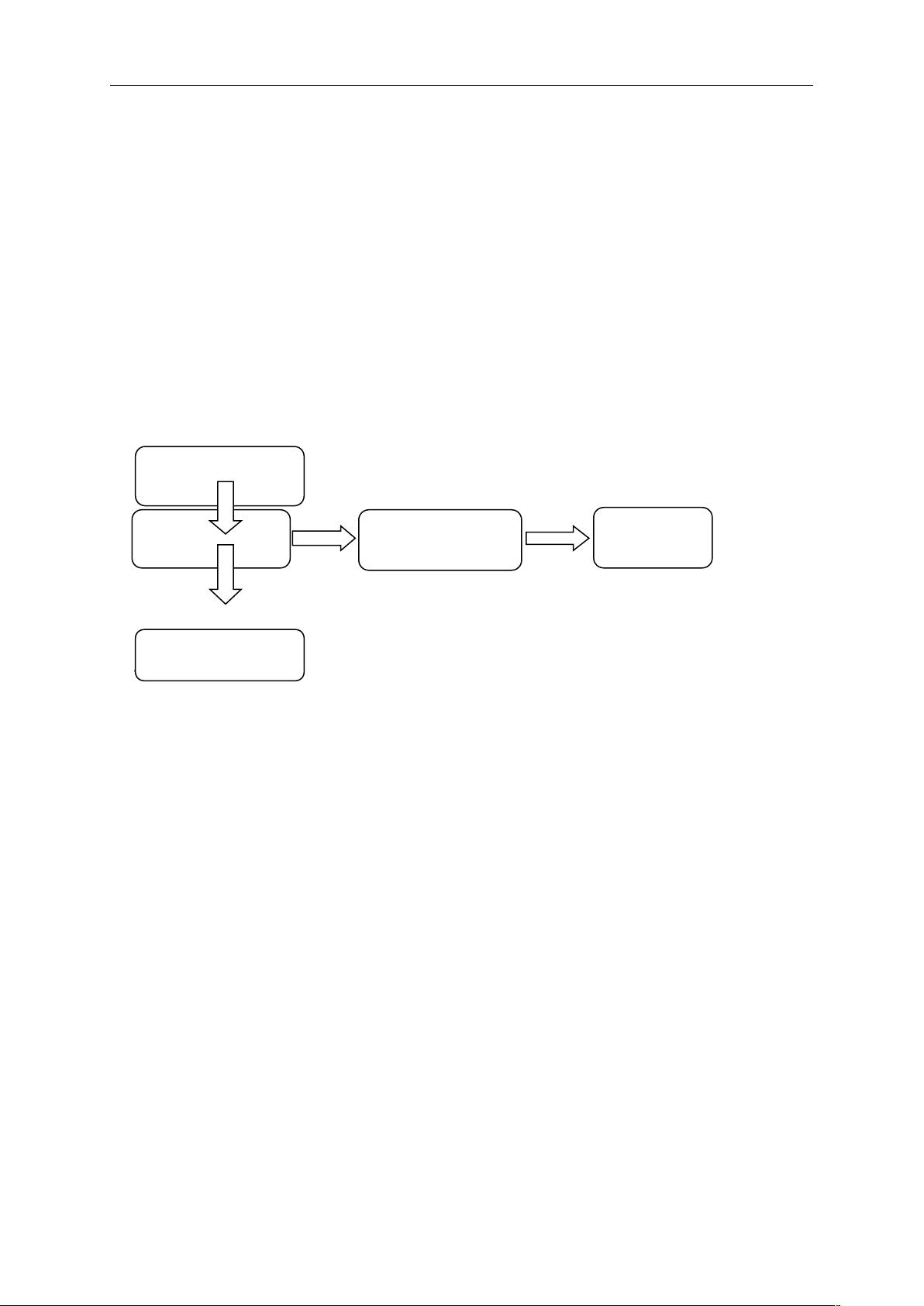

设计要求的定时器具有10秒到24小时59分59秒的定时范围,精度为1秒。系统采用逐位设定预置时间,能够通过六个输入端口分别设定时、分、秒。定时完成后,通过LED数码管显示时分秒信息,并通过声光报警模块发出警告。

2. **单元电路设计**:

- **倒计时部分**:以秒为例,该部分由一个59进制减计数器构成,接收时钟信号(clk),在时钟上升沿启动倒计时。当倒计时达到60秒时,输出一个信号使分计数器减1,直至计时完成。此模块还包括异步复位(res)和使能端(cn),以及数据溢出端(count)和BCD码输出端(dlow, high)。

- **七段数码管显示**:这部分电路接收定时模块输出的BCD码,将其转化为对应的七段码,驱动LED数码管显示当前的时分秒。

3. **软件设计**:

设计过程中,VHDL代码编写完成后,通常会在硬件描述语言仿真工具中进行逻辑仿真,验证设计的正确性。然后,将验证通过的VHDL代码下载到FPGA或ASIC上,通过实际电路进行功能验证。

4. **系统测试**:

在系统测试阶段,会进行功能测试和性能测试,确保定时器能够在实际操作中准确无误地计时,并在定时结束后触发报警。

5. **结论**:

通过VHDL设计的定时器电路,实现了预定功能,简化了硬件结构,提高了系统的稳定性和可靠性。设计能够满足长时间、高精度的定时需求,并且有直观的显示和明确的报警机制。

6. **参考文献**:

可能包含用于设计和实现定时器的相关参考资料和技术文档,这些文献可能涵盖了VHDL语言的基础、数字逻辑设计原理以及特定FPGA或ASIC的使用指南。

这个定时器设计展示了VHDL在数字逻辑系统设计中的强大能力,能够实现复杂的计时和控制功能,同时也体现了硬件描述语言在现代电子系统设计中的重要地位。

1638 浏览量

215 浏览量

2021-10-10 上传

279 浏览量

283 浏览量

265 浏览量

279 浏览量

wenvslan

- 粉丝: 0

最新资源

- WebDrive v16.00.4368: 简易易用的Windows风格FTP工具

- FirexKit:Python的FireX库组件

- Labview登录界面设计与主界面跳转实现指南

- ASP.NET JS引用管理器:解决重复问题

- HTML5 canvas绘图技术源代码下载

- 昆仑通态嵌入版ASD操舵仪软件应用解析

- JavaScript实现最小公倍数和最大公约数算法

- C++中实现XML操作类的方法与应用

- 设计编程工具集:材料重量快速计算指南

- Fancybox:Jquery图片轮播幻灯弹窗插件推荐

- Splunk Fitbit:全方位分析您的活动与睡眠数据

- Emoji表情编码资源及数据库查询实现

- JavaScript实现图片编辑:截取、旋转、缩放功能详解

- QNMS系统架构与应用实践

- 微软高薪面试题解析:通向世界500强的挑战

- 绿色全屏大气园林设计企业整站源码与多技术项目资源