这篇复习资料涵盖了多个IT领域的核心知识点,包括逻辑设计、时序逻辑、主存储器、MIPS汇编语言、处理器设计、Cache、虚拟内存(VM)、总线与I/O接口,以及中断和DMA方式。以下是这些知识点的详细说明:

1. **组合逻辑设计**

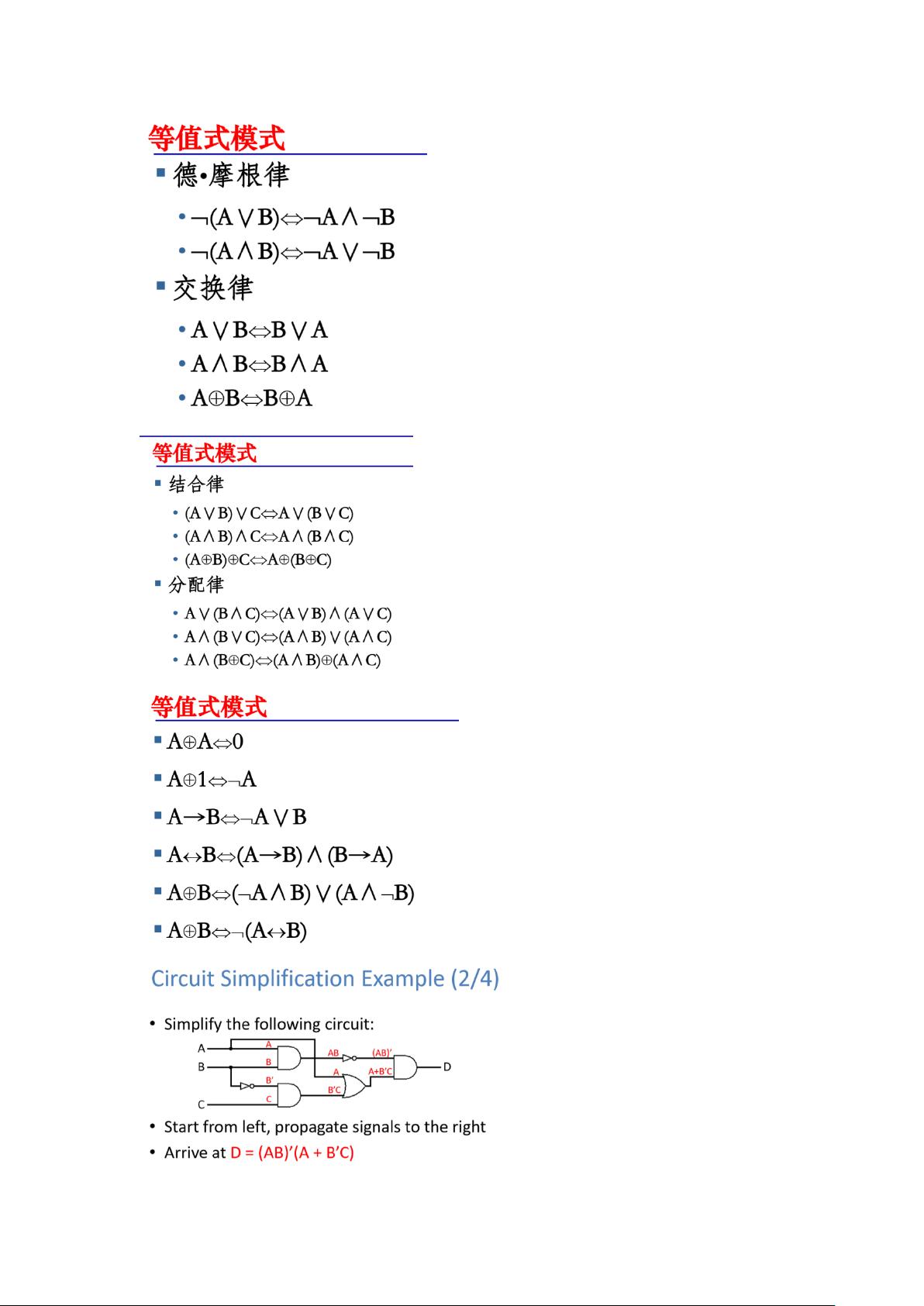

- **布尔代数** 是逻辑设计的基础,它包括最小项和最大项的概念,以及通过合并乘积项、吸收项、配项法和卡诺图进行逻辑函数表达式的化简。

- **基本逻辑部件设计** 如多路选择器,可以利用布尔代数的规则来构造复杂的逻辑功能,例如通过不同的输入组合选择不同的输出。

2. **时序逻辑设计**

- **有限状态机** 分为Moore和Mealy类型,其中Moore的状态输出仅取决于当前状态,而Mealy的状态输出同时取决于当前状态和输入信号。

- **序列选择器** 通过状态转换表来设计次态逻辑和输出逻辑,实现特定序列的识别和处理。

3. **主存储器**

- 存储器扩展涉及混合扩展技术,关键在于正确处理片选信号(CS)。

- **DRAM的刷新** 是为了保持数据完整性,需要定期对DRAM单元进行刷新操作。

4. **MIPS汇编语言**

- MIPS指令集包括R型、I型和J型指令,例如`jr`指令用于跳转。

- 寻址方式包括立即数、寄存器、基址、PC相对寻址和伪直接寻址等。

5. **处理器设计**

- **流水线处理器** 设计中要解决数据冒险和控制冒险,可能需要指令级数据转发、分支预测和暂停等策略。

- **流水线时空图** 描述了指令在流水线各阶段的执行时间。

6. **Cache**

- **局部性原理** 指出程序执行倾向于集中在小范围的数据和指令上,Cache设计基于此原则提高访问效率。

- **Cache映射机制** 常见的有直接映射、组相联和全相联,组相联是常见的一种方式。

7. **虚拟内存(VM)**

- VM允许程序运行在大于实际物理内存的地址空间上,通过虚实地址转换实现。

- **页表** 和**TLB(Translation Lookaside Buffer)** 是实现虚实地址转换的关键组件。

8. **总线与I/O**

- 数据传输方式有**程序查询**、**中断**和**DMA**,中断方式相比函数调用,无需指令即可响应外部事件。

9. **基本概念的选择填空**

- 题目涉及组合逻辑、时序逻辑、指令系统、汇编系统、存储系统、CPU分析等方面的基础知识。

10. **Cache参数计算**

- **写分配** 指当数据写入Cache时,同时写入主存。

- **非写分配** 直接将数据写入主存,不更新Cache。

- Cache的连通性、大小计算、块大小、索引位数和标签位数的确定,涉及对Cache结构的理解和计算。

以上知识点是IT专业课程中的重要内容,理解和掌握它们对于深入学习计算机体系结构和操作系统至关重要。