四路数字抢答器的电路设计与功能解析

在本项目中,设计了一个四路数字抢答器,旨在满足比赛中的抢答需求,包括以下几个关键部分:

1. 抢答器电路 (单元电路设计)

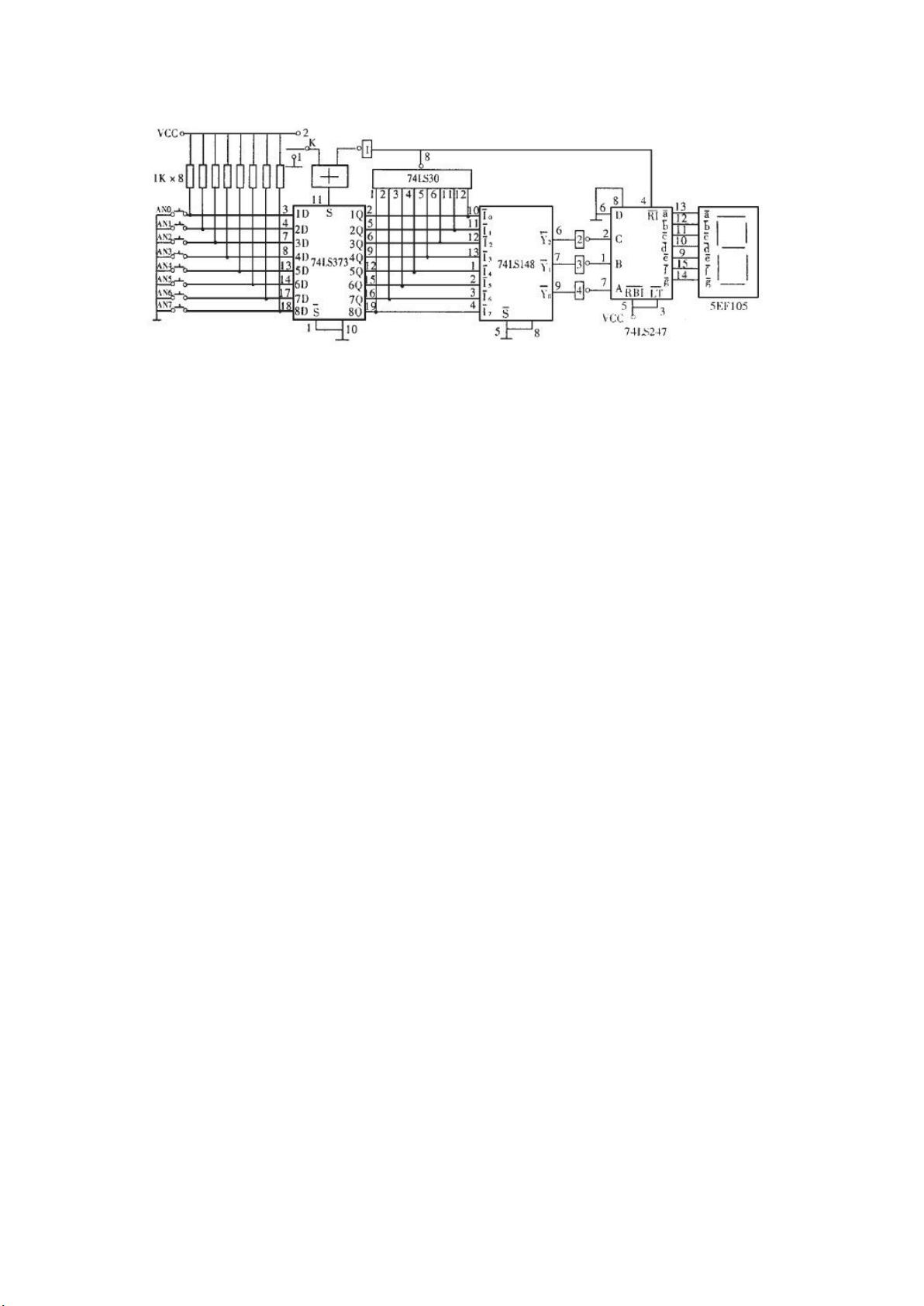

- 电路设计参考图11、2,采用74LS148作为8线-3线优先编码器。当开关S置于"清除"位置时,所有触发器置零,编码器处于待机状态。按下抢答键后,触发优先级电路工作,显示出第一个抢答者的编号,同时锁定其他按键,防止重复抢答。若要再次开始,需主持人手动重置。

2. 定时电路

- 为了适应不同难度的抢答题,使用74LS192同步加减计数器实现可预置时间的功能。主持人设置好抢答时间后,计数器由秒脉冲电路提供时钟,确保公平公正的抢答机会。

3. 报警电路

- 报警电路由555定时器和三极管组成,用于在抢答时间结束时发出警示。多谐振荡器根据电路参数工作,当预设条件满足时,驱动扬声器发出声音。

4. 时序控制电路

- 作为系统的核心控制部分,时序控制电路负责管理抢答和定时流程。当主持人拨到"开始"位置,抢答和定时进入工作状态;选手按下抢答键时,系统暂停;当抢答时间结束后且无人抢答,扬声器会响起提示音。

5. 其他功能

- 抢答者输入锁定电路确保抢答者的优先权,同时计分电路和犯规电路负责计分和违规判断。整个设计还包括安装和仿真步骤,以及最后撰写设计报告。

这个四路数字抢答器系统不仅包含了硬件设计,还涵盖了逻辑控制与时间管理等要素,旨在为比赛提供高效、公平的抢答体验。

2009-05-23 上传

2008-12-28 上传

2011-01-08 上传

2022-12-25 上传

2016-09-12 上传

2009-07-08 上传

qiuzhen11s

- 粉丝: 0

- 资源: 9

最新资源

- mapgis组件开发

- wireshark编译指南

- AIR教程-AIR教程

- 最新EJB 3.0实例教程

- 3天学透ActionScript

- Python 中文手册 v2.4

- 酒店管理系统--论文、说明书、数据库设计

- 防范企业数据泄密的六项措施.doc

- Ext2 核心 API 中文详解.pdf

- Estimation of the Bit Error Rate for Direct-Detected OFDM system

- Oracle+9i&10g编程艺术:深入数据库体系结构.pdf

- AIX 傻瓜教程UNIX

- 2008微思网络CCNP(BSCI)实验手册

- 《Full Circle》中文版第十二期

- SQL Server 2008基础知识

- 中国电信统一视图规范