高速数字电路设计与EMC对策

需积分: 3 106 浏览量

更新于2024-07-31

收藏 1012KB PDF 举报

高速数字电路设计及EMC设计是一门复杂的工程领域,它涉及在高速数据传输系统中的电路设计和电磁兼容(EMC)策略。本文档首先介绍了高速数字信号的基本概念,包括微带线(如Microstrip和 stripline)、同轴电缆、双绞线等,这些是高速电路的重要传输介质,它们对于信号的完整性与干扰控制至关重要。

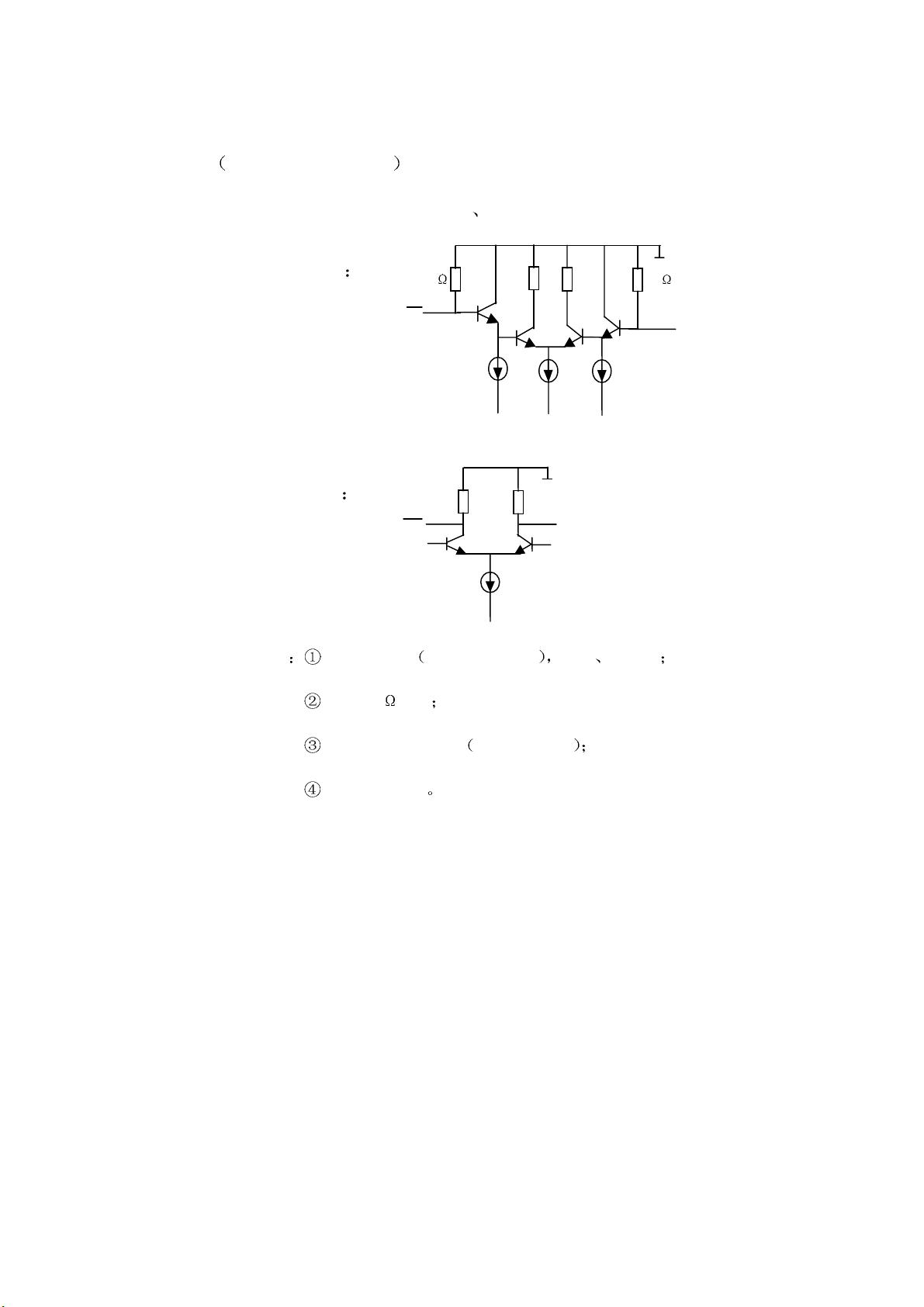

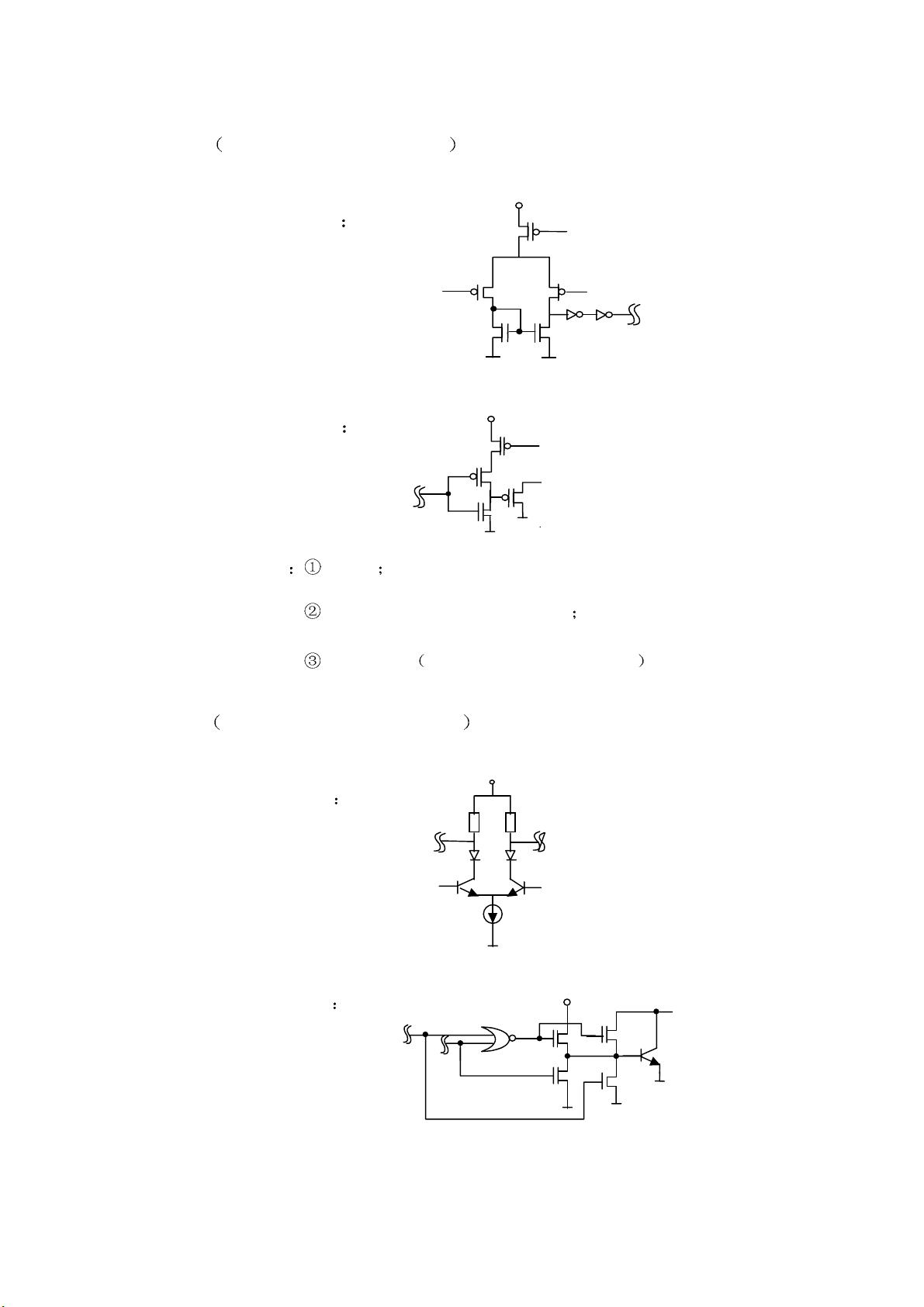

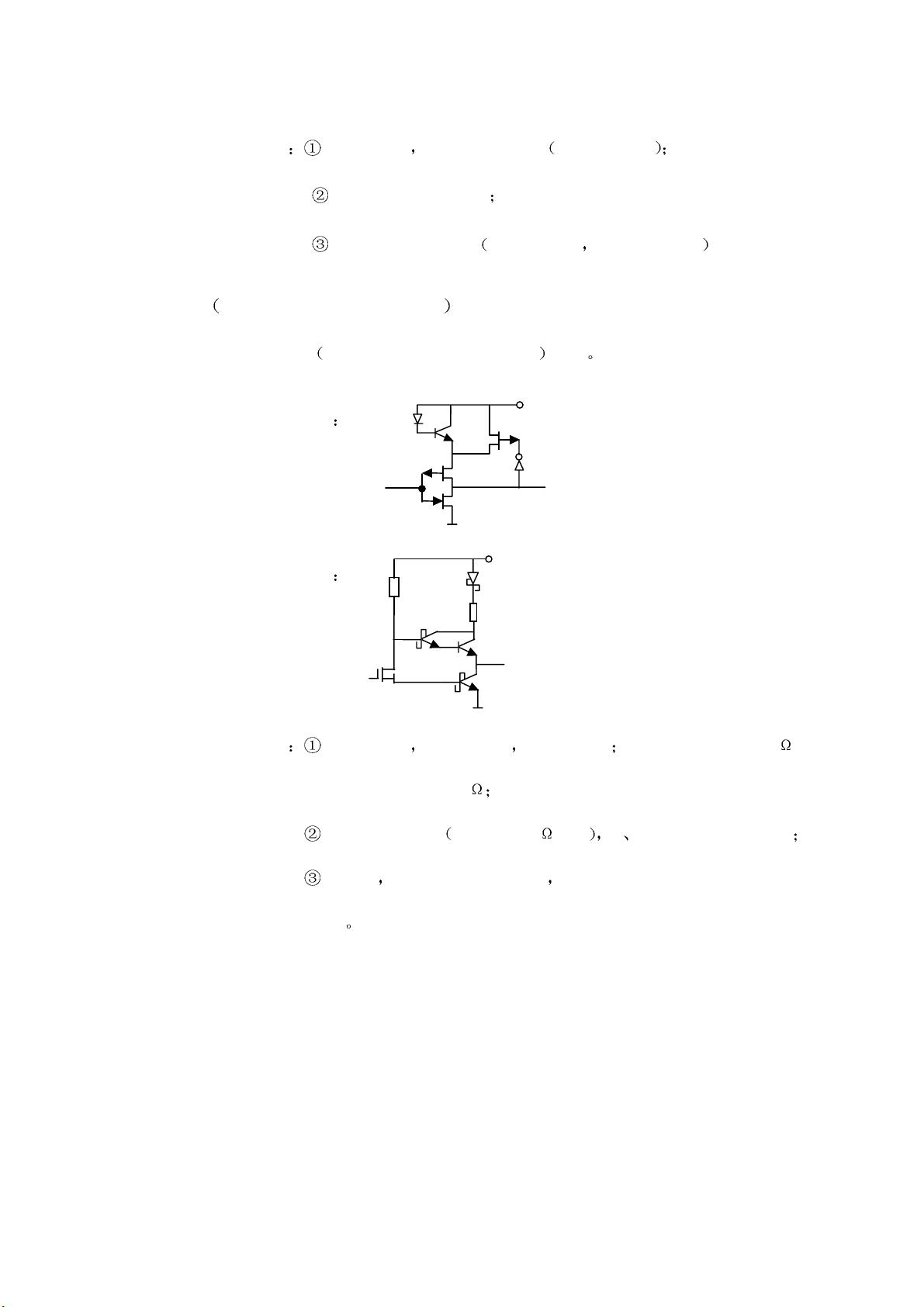

在常见的高速电路设计中,文中列举了ECL(Emitter-Coupled Logic)、CML(Current Mode Logic)、GTL(Gunn Transceiver Logic)、BTL(Backplane Transceiver Logic)、TTL(Transistor-Transistor Logic)等逻辑电路类型,以及模数转换电路,强调了不同电路在高速应用中的特性和匹配策略。例如,电路匹配措施包括反射、终端匹配、始端匹配,这些旨在减少信号失真和反射,提高信号质量。

设计高速电路时,需要遵循一些基本原则,如同步逻辑设计,考虑到器件的输入输出特性,可能需要在功耗和性能之间做出权衡。对于高频率(300MHz以上)信号,推荐使用互补逻辑来降低对电源的需求。信号布局要考虑电流的流向,确保信号路径与电源和地层的正确隔离,并且实施有效的电源滤波,以减少噪声。走线延迟的计算和低速器件的选择也是设计过程中的关键要素。

此外,文档还提到了测试方法,如使用具有50欧姆输入阻抗的高速示波器,以及注意事项,如测量信号应在实际使用位置附近进行,避免测量输出端的信号波形差异。文中还讨论了数字系统中常见的噪声问题,如ringing(振铃)、crosstalk(串扰)和radiated noise(辐射噪声),以及功率谱密度分析,指出大部分信号能量集中在特定频率范围内。

最后,对于FR4 PCB(印刷电路板)设计,特别强调了外层走线延迟的重要性,通常在140到1ns之间。高速数字电路设计及EMC设计是一门技术密集型的工作,需要深入理解信号传输原理、电路特性和噪声控制策略,以实现高效、可靠的高速数字通信。

103 浏览量

2022-09-06 上传

2022-09-24 上传

155 浏览量

140 浏览量

点击了解资源详情

点击了解资源详情

点击了解资源详情

herolxy2008

- 粉丝: 0

- 资源: 1

已收录资源合集

已收录资源合集