高速数字电路设计与EMC实践指南

需积分: 10 9 浏览量

更新于2024-07-31

收藏 1002KB PDF 举报

"高速数字电路设计及EMC设计" 是一本深入探讨高速数字电路设计及其电磁兼容性(EMC)问题的专业书籍。本书主要涵盖了高速电路的基本概念、常见类型、匹配措施以及设计的一般原则和调试方法。

1. 高速数字信号:高速电路是指在频率较高的情况下操作的电子电路,通常指的是信号频率超过100MHz的电路。这种高频率导致了信号完整性问题,如信号反射、串扰和辐射噪声。

2. 微带线与带状线:这两种是高速电路中常用的传输线形式。微带线是在介质基板上,信号线与接地平面之间有一层空气的传输线,而带状线则将信号线完全包围在介质内部,两侧有接地平面。它们各有优缺点,微带线易于制造但易受环境影响,带状线则有较好的屏蔽效果。

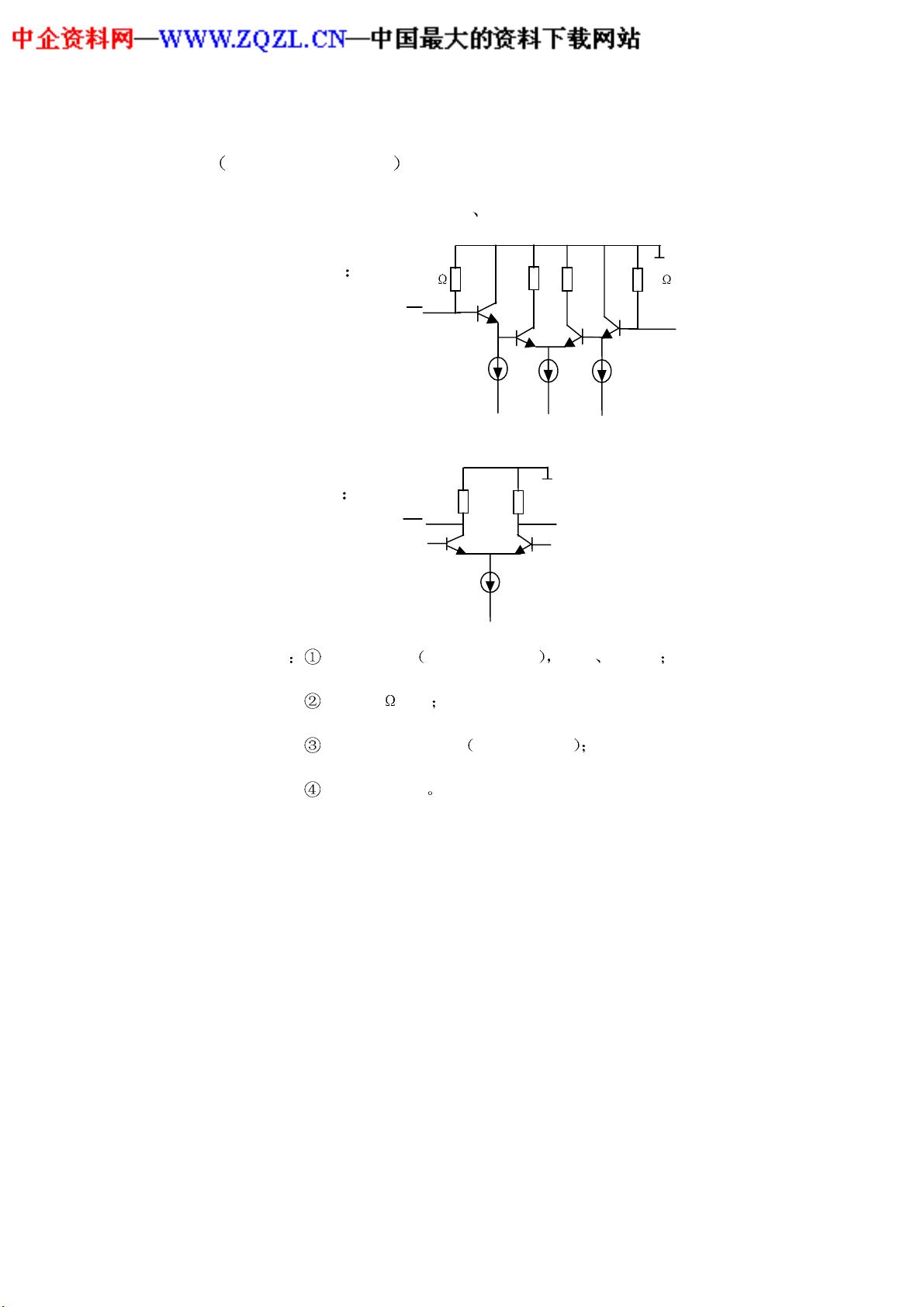

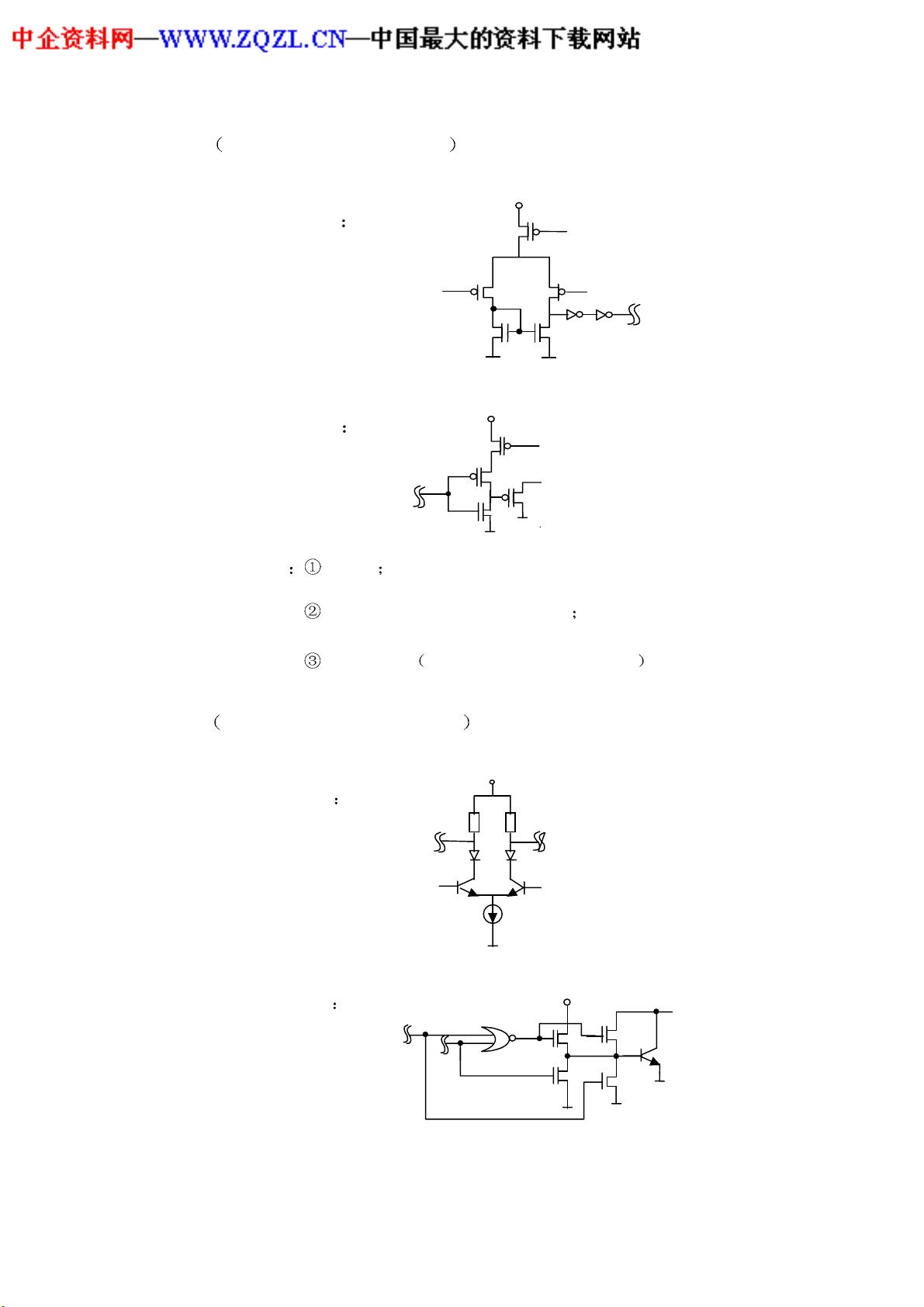

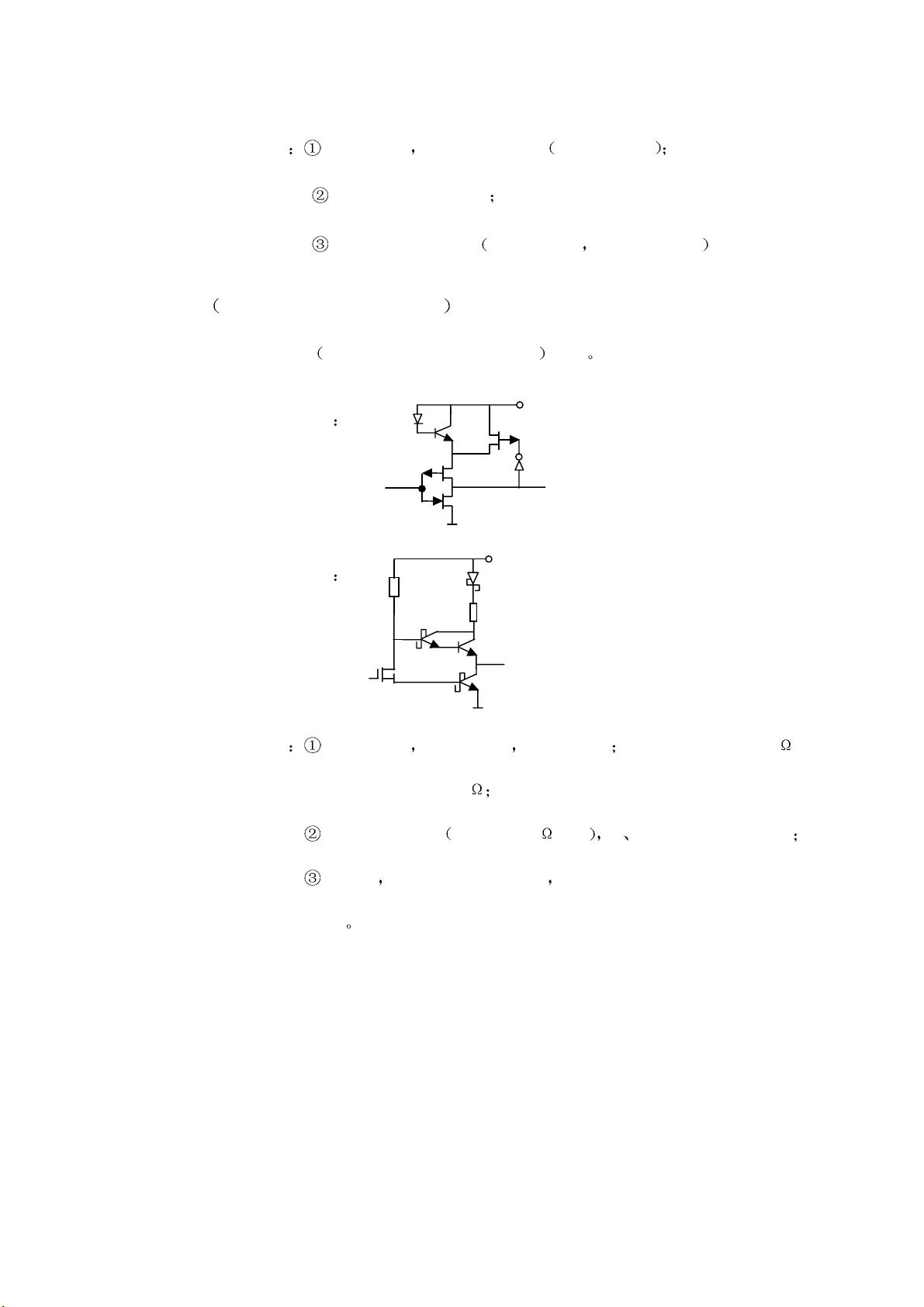

3. 常见高速电路:书中列举了ECL(Emitter Coupled Logic)、CML(Current Mode Logic)、GTL(Gunning Transceiver Logic)、BTL(Backplane Transceiver Logic)、TTL(Transistor-Transistor Logic)等不同类型的逻辑电路,以及模数转换电路和线路接收器。这些电路在不同的应用场景中各有优势,如ECL以高速著称,而TTL则广泛应用在低功耗系统。

4. 电路匹配措施:匹配是高速电路设计中的关键,包括终端匹配(用于消除反射)和始端匹配(防止信号源处的反射)。书中强调了在设计中需考虑到这些匹配策略,以确保信号质量和系统稳定性。

5. 高速电路设计原则:设计者应遵循同步逻辑设计,理解器件的输入输出特性,并选择合适的匹配电路。在考虑功耗的同时,可能需要引入一定程度的失配。对于极高速率信号,互补逻辑常被推荐以降低电源需求。此外,理解电流环路、合理布线、电源滤波、估算信号延迟以及选用低速率器件都是重要的设计准则。

6. 测试方法:为了准确评估高速信号,建议使用50欧姆输入的示波器,并定制探头进行测量。测试点应尽可能接近信号的实际位置,以减少误差。书中还提到了ringing(振铃)、crosstalk(串扰)和radiated noise(辐射噪声)这三种数字系统常见的噪声问题。

7. 信号的功率谱密度:大部分数字信号的能量集中在f_knee频率之内,f_knee定义了信号质量的转折点,对于理解和优化高速信号至关重要。

8. 传输线延迟:书中提及FR4 PCB(印制电路板)的外部迹线延迟大约在140至1ns/英寸,这是设计时必须考虑的因素,以确保信号的正确时序。

本书提供了一个全面的框架,帮助读者理解和解决高速数字电路设计中遇到的挑战,同时关注电磁兼容性的维护,以确保系统的稳定和可靠运行。

111 浏览量

113 浏览量

2022-09-24 上传

167 浏览量

点击了解资源详情

130 浏览量

点击了解资源详情

117 浏览量

yzr1107157853

- 粉丝: 0

最新资源

- 易二维码签到系统:会议活动签到解决方案

- Ceres库与SDK集成指南:C++环境配置及测试程序

- 深入理解Servlet与JSP技术应用与源码分析

- 初学者指南:掌握VC摄像头抓图源代码实现

- Java实现头像剪裁与上传的camera.swf组件

- FileTime 2013汉化版:单文件修改文件时间的利器

- 波斯语话语项目:实现discourse-persian配置指南

- MP4视频文件数据恢复工具介绍

- 微信与支付宝支付功能封装工具类介绍

- 深入浅出HOOK编程技术与应用

- Jettison 1.0.1源码与Jar包免费下载

- JavaCSV.jar: 解析CSV文档的Java必备工具

- Django音乐网站项目开发指南

- 功能全面的FTP客户端软件FlashFXP_3.6.0.1240_SC发布

- 利用卷积神经网络在Torch 7中实现声学事件检测研究

- 精选网站设计公司官网模板推荐