高速数字电路设计与EMC实战指南

需积分: 4 192 浏览量

更新于2024-08-01

收藏 593KB PDF 举报

"高速数字电路设计及EMC设计"

在高速数字电路设计中,理解关键概念和技术至关重要,因为这些因素直接影响到电路的性能、可靠性和电磁兼容性(EMC)。高速数字电路是指工作频率高于100MHz的电路,其中信号传输速度、信号完整性以及电磁干扰(EMI)成为设计的主要考量。

1. 微带线和带状线是高速电路中常见的传输线类型。微带线是在介质基板上,信号线位于上方,与接地平面形成电场分布。带状线则将信号线置于两层接地平面之间,具有更好的屏蔽效果和更低的信号损耗。它们的特性阻抗、衰减和相位速度都取决于结构尺寸、介电常数和材料特性。

2. 同轴线和双绞线也是常见的传输媒介。同轴线由内导体、绝缘介质和外导体组成,提供良好的屏蔽,适用于射频和高频信号传输。双绞线通过两条相互扭绞的导线减少电磁辐射和外部干扰,常用于低速通信。

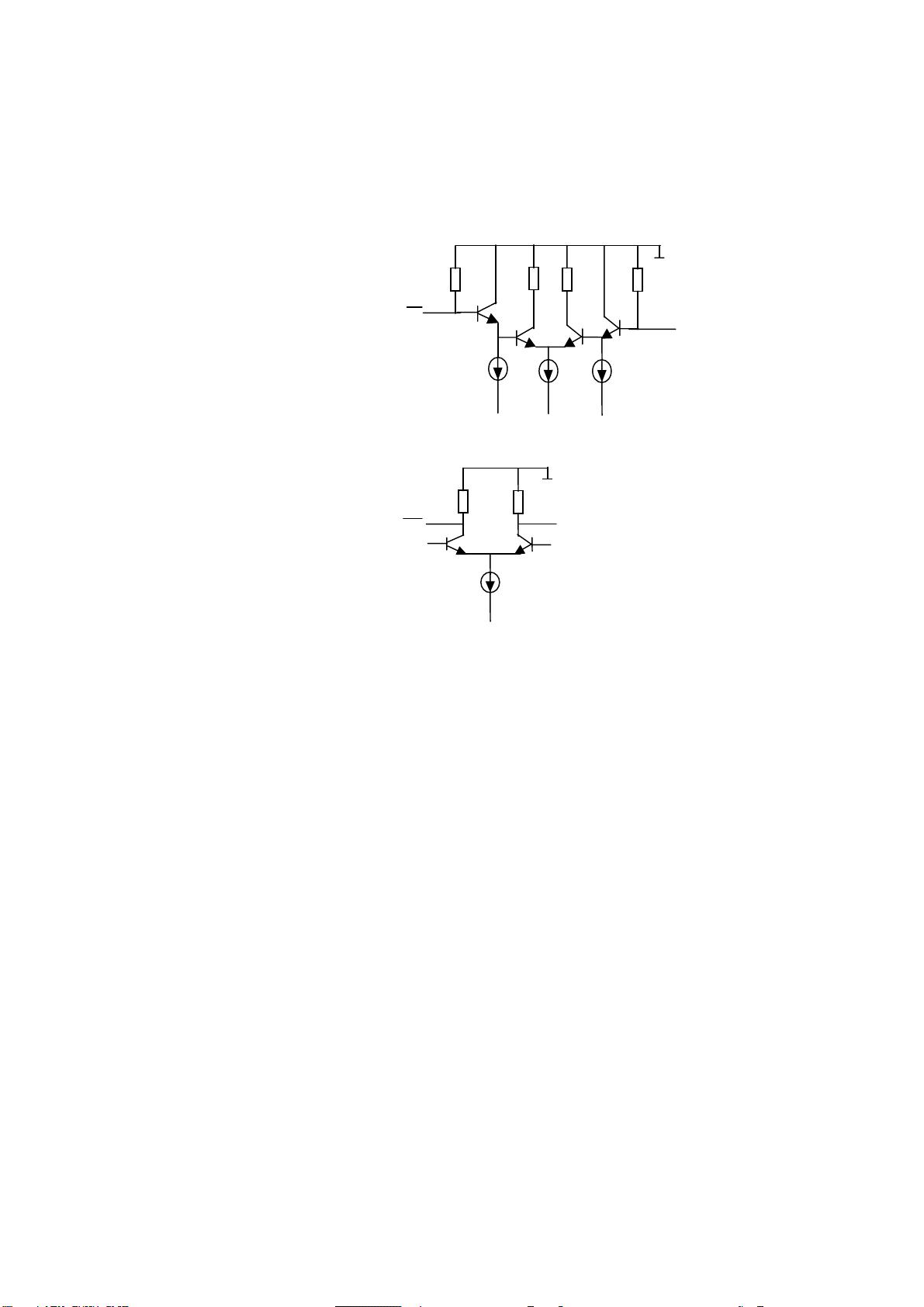

3. 常见的高速电路逻辑标准包括ECL(Emitter Coupled Logic)、CML(Current Mode Logic)、GTL(Gunning Transceiver Logic)、BTL(Backplane Transceiver Logic)和TTL(Transistor-Transistor Logic)。每种逻辑都有其独特的优势和应用场景,例如ECL以其高速度而著名,但功耗较高;CML提供低噪声和低功耗,适用于高速接口。

4. 在高速电路设计中,匹配是非常关键的。反射通常由阻抗不连续引起,可以通过终端匹配和始端匹配来解决,以减少信号损失和反射噪声。终端匹配是为了使负载阻抗与信号源阻抗匹配,而始端匹配则是为了在信号源处消除反射。

5. 高速电路设计原则包括采用同步逻辑以减少竞争和冒险,理解并适应器件的输入输出特性,合理设计电源和地层,以及使用适当的滤波技术以减少噪声。对于极高频率信号,使用互补逻辑可以降低电源需求。此外,了解信号电流路径,确保高速信号有合适的回流路径,同时避免信号线间的串扰。

6. 测试是验证设计的关键步骤。高速示波器和探头的选择至关重要,应尽可能接近信号的实际工作位置进行测量。测试项目包括振铃(ringing)、串扰(crosstalk)和辐射噪声,这些都是数字系统中的主要噪声源。

7. 信号延迟是设计高速电路时必须考虑的因素,尤其是FR4 PCB材料等不同介质对信号传播速度的影响。同时,尽可能选用低工作速率的器件以简化设计,差分线的紧密布局可以提高信号质量。

高速数字电路设计及EMC设计涉及多个层面,包括传输线理论、逻辑标准、匹配网络、信号完整性和电磁兼容性。设计师需要综合考虑这些因素,以实现高效、可靠的高速系统。

103 浏览量

2022-09-06 上传

2022-09-24 上传

158 浏览量

140 浏览量

点击了解资源详情

点击了解资源详情

点击了解资源详情