Xilinx ISE中异步FIFOIP的配置与操作详解

需积分: 50 14 浏览量

更新于2024-07-18

1

收藏 3.17MB DOCX 举报

在Xilinx ISE工具中,异步FIFO IP核的使用是一项重要的技能,特别是在设计涉及不同时钟域通信的系统时。FIFO (First-In-First-Out) 是一种常见的数据结构,用于存储和同步数据流,特别适合处理不同速率或宽度的数据传输问题。本文详细介绍了如何在ISE中创建、配置和使用FIFO IP核。

首先,当你启动新项目并选择Native模式,因为目标不是SoC(System-on-Chip)设计,这表示你将使用FPGA本身的逻辑资源而非预集成的硬件。接着,你需要配置FIFO的关键参数,如时钟类型。由于FIFO通常用于异步读写,即读写操作的时钟不同步,所以选择异步模式至关重要。

存储器类型的选择是另一个关键步骤。块RAM(Block RAM)和分布式RAM(Distributed RAM)是两种常见选项。块RAM是专门为FPGA设计的定制RAM,适用于大容量FIFO,因为它支持不对称读写速度,而分布式RAM则是由LUT(Look-Up Table)实现的,适合小型FIFO。如果要全面理解FIFO功能,建议选择块RAM。

在设置FIFO的具体参数时,写入深度和宽度被定义为256位和8位,而读取宽度设为4位,深度则会根据这些参数自动计算。值得注意的是,实际的写入深度(actualwritedepth)和读取深度(actualreaddepth)可能会小于预期,这是因为在实际操作中可能受到硬件资源限制。这部分内容将在后续的代码示例和原理讲解中深入探讨。

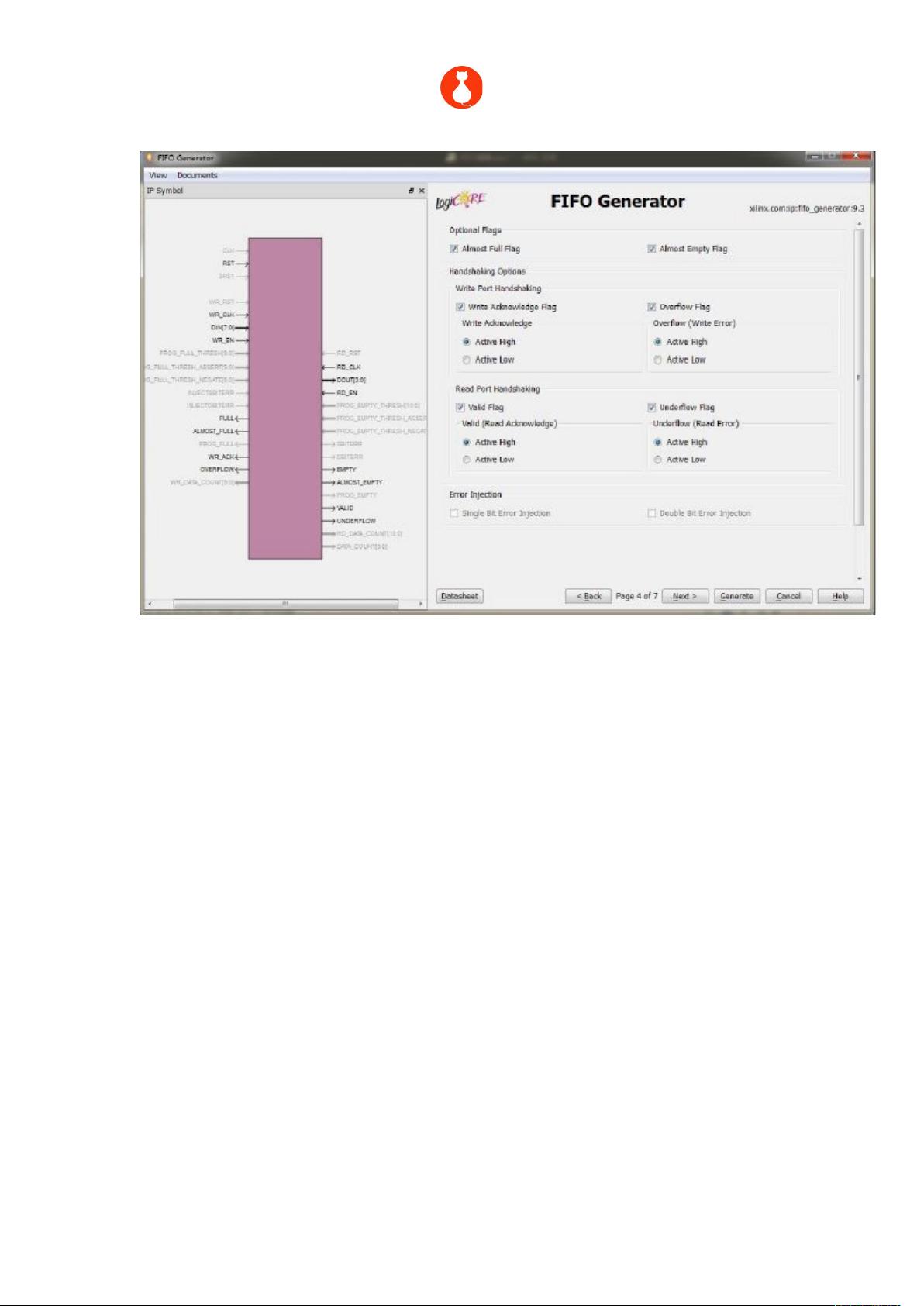

添加FIFO的信号是为了增强灵活性和控制能力,尽管这会增加复杂性。包括但不限于使能信号、读写标志、满/空指示等,它们有助于跟踪FIFO的状态和控制数据的进出。此外,复位信号和可编程信号的配置也必不可少,它们允许对FIFO的行为进行初始化和动态调整。

通过使用ISE中的FIFO IP核,设计师能够有效地解决跨时钟域的数据交换问题,并且深入了解信号的工作机制,这对于高效利用FPGA资源和优化系统性能具有重要意义。学习和掌握这一技术对于从事FPGA开发的工程师来说是一项基础且实用的技能。

859 浏览量

1823 浏览量

2024-10-15 上传

2022-09-24 上传

966 浏览量

127 浏览量

小明同学@zx

- 粉丝: 9

- 资源: 8

最新资源

- win_udp:Windows网络udp框架服务器和侦听器

- 如何规划团队训练课程PPT

- torch_cluster-1.5.5-cp36-cp36m-linux_x86_64whl.zip

- 取Excel表格有数据单元格的起讫行列.rar

- zencharts:将 High Charts 库的强大功能与 Zendesk Developer API 相结合的小型应用程序

- wild-rydes:野生莱德

- Redosnap Launcher-crx插件

- CNN_for_brain_ventricles_segmentation:“个人3D脑图集”项目。 利用全卷积神经网络对大脑的CT数据进行分割

- 批量修改文件名.zip

- 取Excel表格有数据单元格的起讫行、列.rar

- html2text:用 Go 编写的 html 到文本转换器

- torch_scatter-2.0.4-cp37-cp37m-win_amd64whl.zip

- Email Notifier-crx插件

- yun-text:“云杯”景区声誉评价得分预测中第三个解决方案的DL部分

- milestoneproject2-memorygame:一种记忆游戏,要求用户匹配隐藏在牌组中的成对纸牌

- Android Binder通信案例