Lattice ispMACHTM 4000V/B/C/Z设计详解与常见问题解析

需积分: 9 28 浏览量

更新于2024-08-02

收藏 2.34MB DOC 举报

Lattice ispMACHTM 4000V/B/C/Z设计指南是一份详尽的技术文档,针对Lattice公司出品的这款高性能、低功耗 CPLD(复杂可编程逻辑器件)系列提供了全面的设计指导和常见问题解答。该指南分为多个部分,旨在帮助设计师充分利用ispMACHTM 4000系列器件的优势。

首先,章节1介绍了ispMACHTM 4000的特点,包括其超快的性能和极低的功耗,强调了产品的核心优势。产品系列的选择与器件选择手册是后续设计的基础,设计师可以根据项目需求选择适合的器件型号。

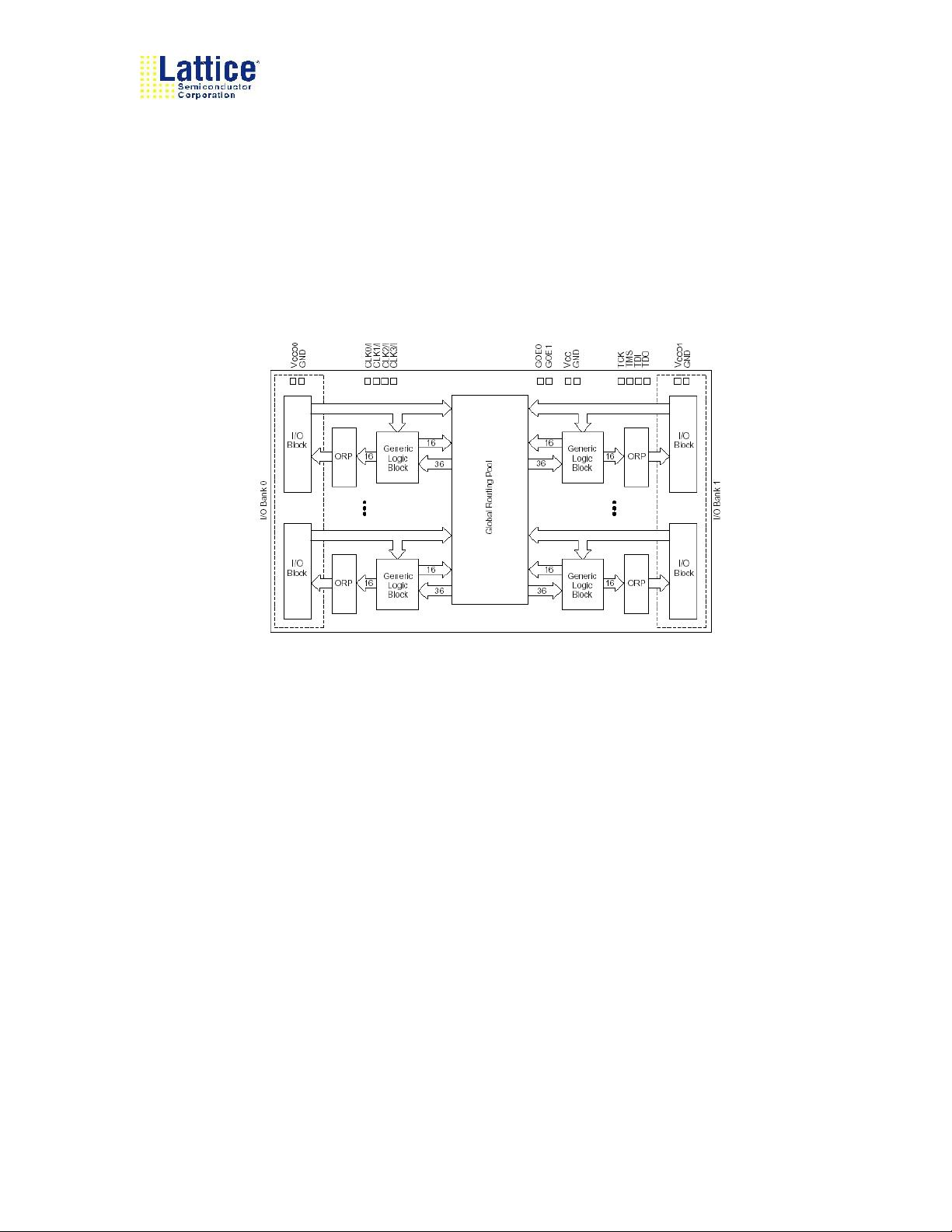

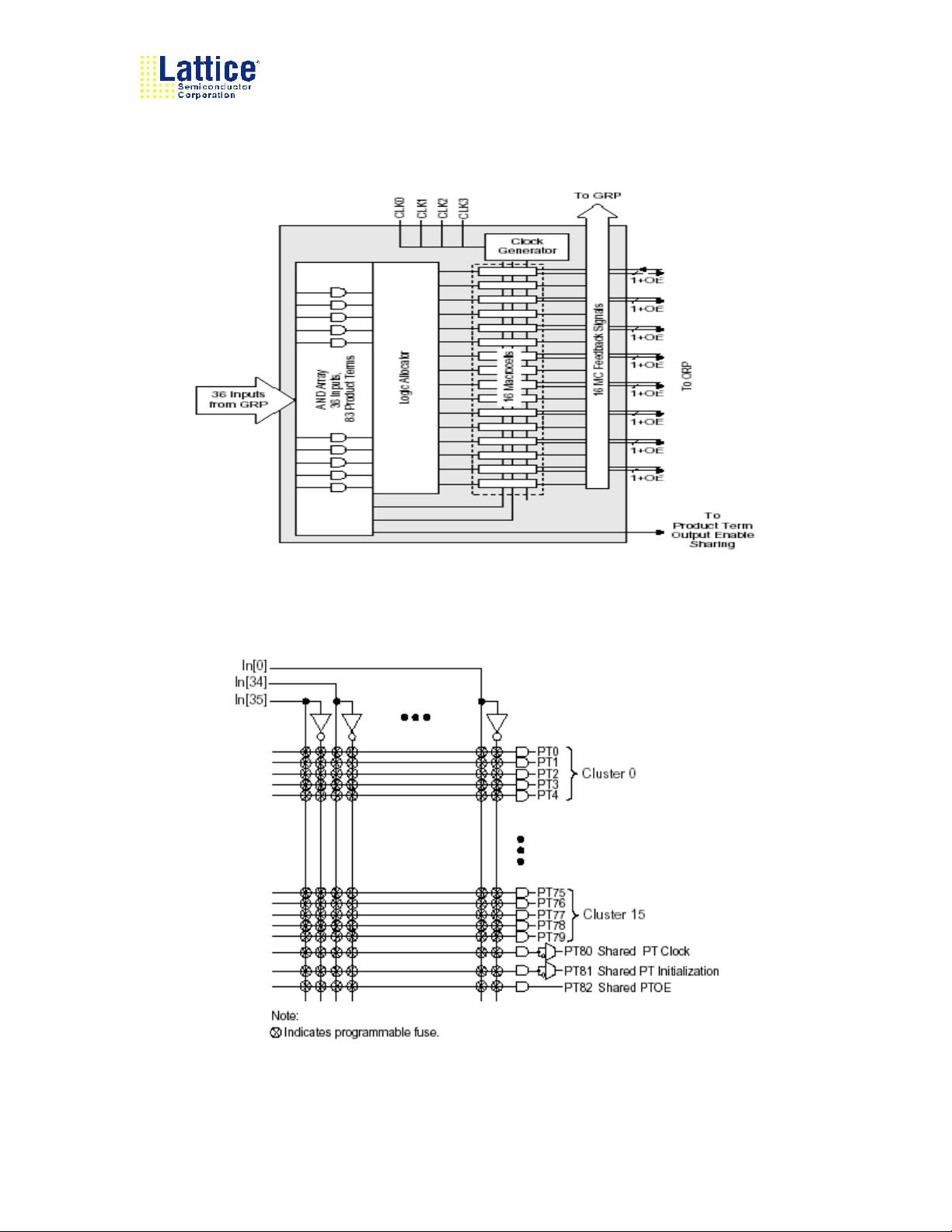

在体系结构概述部分(2.1),详细阐述了ispMACH4000的架构,包括逻辑分配器、三种速度路径、带可编程延时的输入寄存器、灵活的时钟和时钟使能机制等关键组件。这些特性使得设计者可以精确地定制其逻辑行为和时序。

设计实现阶段(3.1-3.4)涵盖了全局约束、Fitter选项、利用率设置、约束编辑器的使用以及优化设计的方法。设计师需要理解如何正确配置Fitter选项以达到最优的布线和资源分配,同时注意设备设置表、封装查看、引脚编辑规划等步骤的重要性。

针对实际应用,指南列举了诸如电源管理(VCC和VCCO)、上电时间和电源复位、时钟使用规范、全局输出使能、双向I/O接口注意事项、未使用引脚处理、I/O电平设置等关键要点,确保设计的稳定性和可靠性。

此外,还涉及了功耗计算、温度计算、热插拔特性、ispJTAG编程/测试信号、CPU加载频率限制、以及综合工具选择等实用信息,为设计师提供了全面的设计指导。

最后,关于约束文件的管理和嵌入式ModelSim仿真技术的使用,以及ModelSim应用的建议,帮助设计师在设计流程中有效地进行验证和调试。

这份指南为Lattice ispMACHTM 4000V/B/C/Z的设计者提供了全面且深入的技术支持,涵盖了从器件选择到实际应用的各个环节,旨在提高设计效率并确保最终产品的性能和稳定性。

2021-01-19 上传

270 浏览量

196 浏览量

2024-10-11 上传

194 浏览量

2024-12-28 上传

2024-11-07 上传

200 浏览量

g360883850

- 粉丝: 86

- 资源: 18

最新资源

- MATLAB在图像处理技术方面的应用论文

- 回溯算法 用来设计货箱装船、背包、最大完备子图、旅行商和电路板排列问题的求解算法。

- 有关贪婪算法的一篇文章

- 2410-S实验指导书.pdf

- makefile PDF 经典电子书

- 嵌入式CC++语言精华文章集锦

- visual studio .NET 技术手册

- 测试用例设计指南说明

- 正交试验设计测试用例

- 中软终端安全解决方案

- Python Essential Reference (3rd Edition)

- The Art of Unix Programming

- Linux内核完全注释-3.0

- 自考英语2的复习知识重点难点

- 全国计算机等级考试三级C语言上机100题

- 蓝屏代码 蓝屏代码 详解