SDRAM内存原理与时序详解:Bank与位宽构造

需积分: 9 199 浏览量

更新于2024-07-29

收藏 1.33MB PDF 举报

SDRAM,全称同步动态随机访问存储器(Synchronous Dynamic Random Access Memory),是一种广泛应用于计算机系统的内存类型。其原理和时序设计对于理解计算机内存工作至关重要。

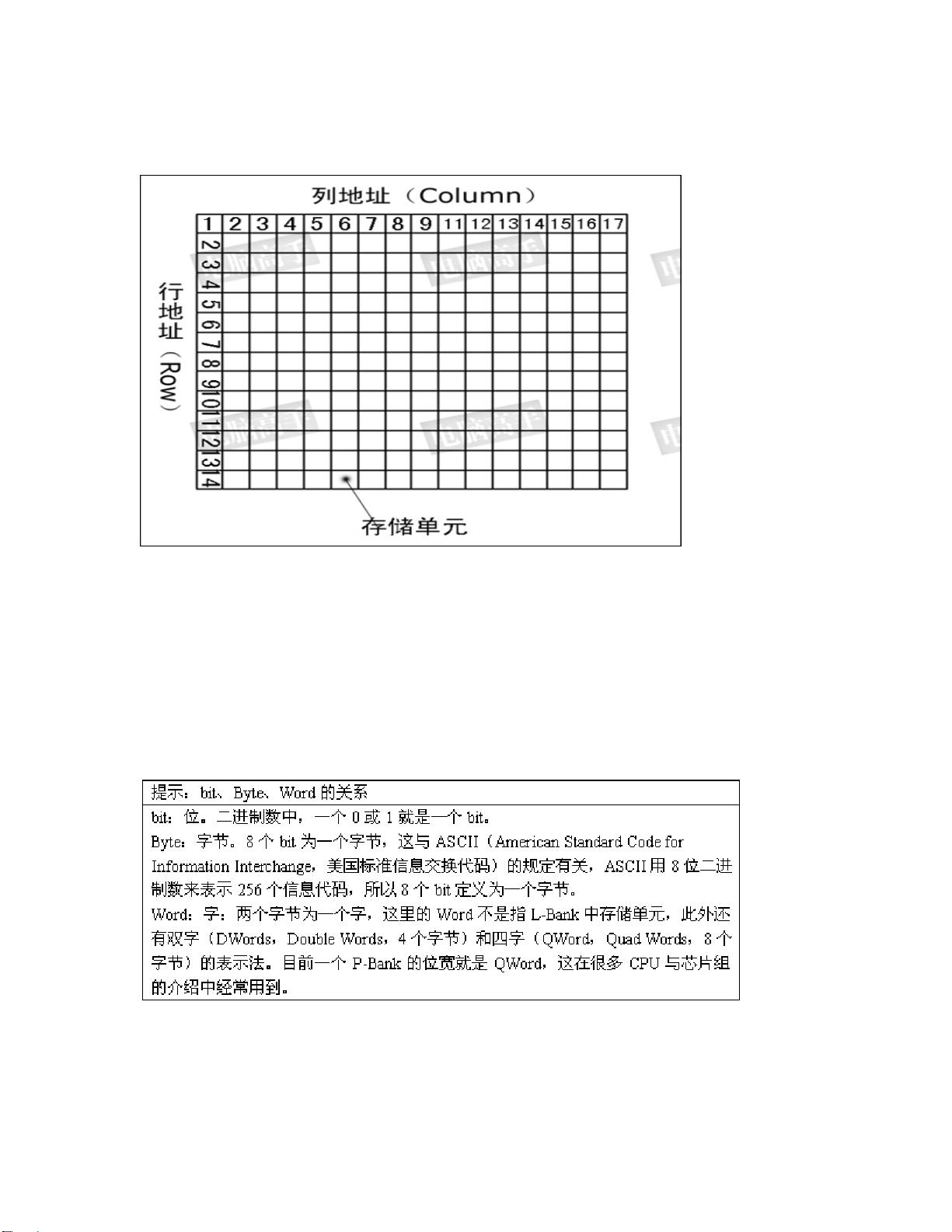

首先,SDRAM内存模组的基本结构是由物理Bank(PhysicalBank,P-Bank)构成的。物理Bank的概念起源于早期的内存系统设计,旨在确保CPU在单个时钟周期内能够接收完整的数据。CPU的数据总线宽度决定了所需数据的容量,即P-Bank的位宽。例如,早期的Pentium处理器需要两条72-pin SIMM内存,每条只能提供32-bit的位宽,而Pentium的64-bit数据总线需求则需要更高的内存配置。

在SDRAM时代,每个内存芯片自身具有一定的位宽,如台式机市场常见的是8-bit或16-bit芯片。为了匹配CPU的数据总线位宽,需要通过并联多个芯片来组合成一个P-Bank。比如,16-bit芯片需要4颗来实现64-bit的P-Bank,而8-bit芯片则需要8颗。这样做的目的是优化内存性能,确保数据传输效率。

然而,随着计算需求的增长,单个P-Bank的容量已经无法满足系统的需求。因此,现代的芯片组支持多个P-Bank,允许用户根据需要选择不同的Bank进行数据访问。这种设计允许系统同时处理多个独立的数据流,提高了整体性能和灵活性。

SDRAM的时序参数包括读写延迟时间(CL,Column Address Latency)、预充电时间(RP,Row Precharge Time)、行保持时间(RAS,Row Active to Precharge Time)和列地址刷新时间(CAH,Column Address Hold Time)。这些时序参数对于内存的实际操作至关重要,它们定义了内存的响应速度和数据一致性。优化这些参数有助于减少内存延迟,提高系统性能,尤其是在高速缓存和频繁数据交换的场景下。

SDRAM的工作原理和时序管理涉及到内存模块的构建、内存芯片的位宽选择、以及如何适应CPU数据总线的需求,这些都是保证计算机系统稳定高效运行的关键要素。随着技术的进步,未来的内存架构可能会进一步优化这些细节,以应对不断增长的计算挑战。

2010-01-14 上传

2011-12-07 上传

2013-07-31 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

2013-07-29 上传

2008-11-16 上传

anchungang

- 粉丝: 0

- 资源: 8

最新资源

- AS3TuningInsideAVM2JIT.pdf

- J2ee开发中过滤器的使用

- JAVA 23设计模式一点就通

- 简易秒表 AT89C51

- 关于统一建模语言(UML, Unified Modeling Language)的一本全面实用的参考

- JavaScript.DOM编程艺术.pdf

- 社会劳动保障系统(Word文档)

- Oracle PL SQL Programming

- makefile(中文版).pdf

- The Cambridge Dictionary of Statistics (3rd Edition)

- IEEE802.3-2005版标准文件4

- opnet网络仿真最新版

- LoadRunner性能测试实战

- Windows文件系统过滤驱动开发教程(第二版)-楚狂人.pdf

- Data Mining With R

- AD7715 在精密分析仪器中的应用研究