飞思卡尔i.MX6 DDR3平台DRAM高级应用调试指南

飞思卡尔i.MX6平台DRAM接口高阶应用指导专著于针对飞思卡尔i.MX6处理器的高级应用,其中着重讨论了DDR3内存模块的集成和优化。此篇文档详细介绍了在i.MX6平台上有效利用官方工具进行DDR3内存的配置、初始化和测试的相关知识。

首先,设计考虑是关键,包括但不限于飞思卡尔提供的"HWDesignCheckingListfori.Mx6"文档中的硬件设计要点。设计师需遵循严格的规则,如确保i.MX6和DDR3芯片的ZQ引脚连接精确至1%精度的240欧姆电阻,为DRAM_VREF提供低噪声且稳定的50% NVCC_DRAM电压,以及正确处理DRAM_RESET信号的接地和电阻设置。同时,文档强调了差分时钟接口的设计规范,如DQS和CLK信号的差分100欧姆阻抗控制,以及数据、地址和控制信号线的单端50欧姆阻抗匹配。

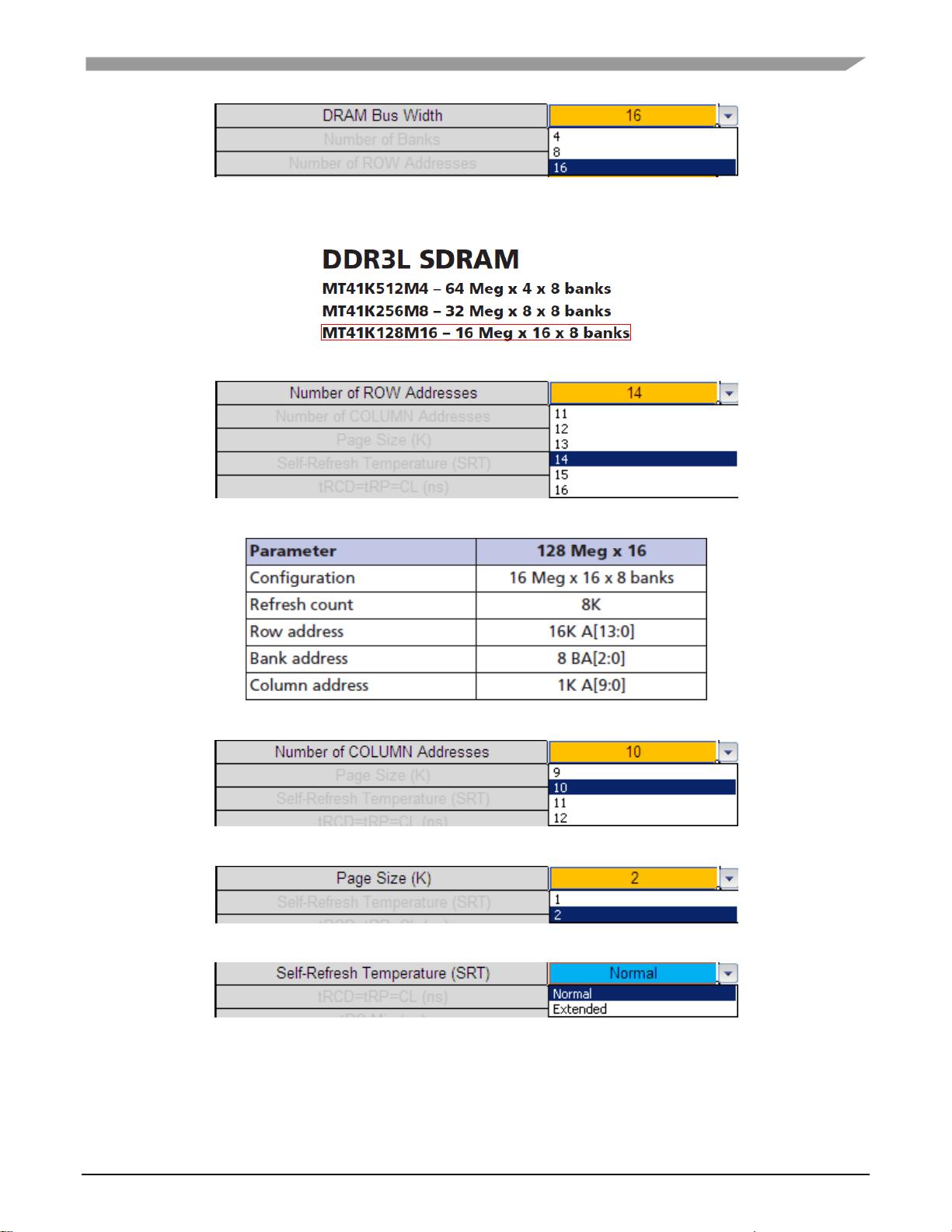

DDR3初始化代码生成工具是另一个核心部分,它帮助用户生成定制化的DDR3初始化脚本,确保内存与i.MX6平台的兼容性和最佳性能。通过这个工具,开发者可以有效地管理内存配置,如时序参数设置、纠错功能和刷新策略等。

此外,文档还提到了DDR3自校准和压力测试工具,这些工具用于检测内存的稳定性和可靠性,以预防潜在的问题并优化系统性能。自校准确保内存模块达到最佳工作状态,而压力测试则能模拟极限条件下的操作,以便提前发现并修复可能存在的故障隐患。

最后,文档推荐进一步阅读以获取更深入的硬件设计和调试技巧,这可能是飞思卡尔社区或其他相关技术资源,以供读者扩展知识和解决实际项目中的问题。

本篇指南为飞思卡尔i.MX6平台的DDR3内存设计者提供了详尽的实践指导,涵盖了从设计原则到具体工具使用的全过程,确保了高效、稳定和可靠的内存集成。对于从事i.MX6平台开发的工程师来说,理解和遵循这些指导至关重要。

2019-05-07 上传

2020-09-11 上传

点击了解资源详情

2020-07-27 上传

2021-09-25 上传

136 浏览量

2021-09-25 上传

luerlyhs

- 粉丝: 55

- 资源: 30

最新资源

- SVR:简单向量回归-Udemy

- AquariumHoodLEDController

- Code,java论坛源码,java消息队列订单

- TRIDIEGS:求对称三对角矩阵的特征向量的特征值。-matlab开发

- get_html_source_gui:获取网页源代码GUI代码与重组程序

- json-builder:json-parser的序列化副本

- 参考资料-附件1-9-补充协议-新增.zip

- 共享计时器:一种Web应用程序,您可以在其中创建并与其他人共享计时器。 建立在React Hooks和Firebase之上

- spotify_battle

- maistra-test-tool:在OpenShift上运行maistra任务的测试工具

- mobi_silicon

- CrawlArticle:基于文字密度的新闻正文提取模块,兼容python2和python3,替换新闻网址或网页开源即可返回标题,发布时间和正文内容

- uu,java源码学习,springboot的源码是java

- regexp_parser:Ruby的正则表达式解析器库

- Get15

- Mary Poppins Search-crx插件