IC封装工艺是集成电路制造过程中的重要环节,它涉及到芯片(Die)与各种框架(L/F)、塑封材料(EMC)结合成不同外形的封装体。这个工艺流程包括以下几个关键步骤:

1. **IC设计**:这是整个过程的起点,由设计者创建电路图并定义芯片的功能和性能需求。

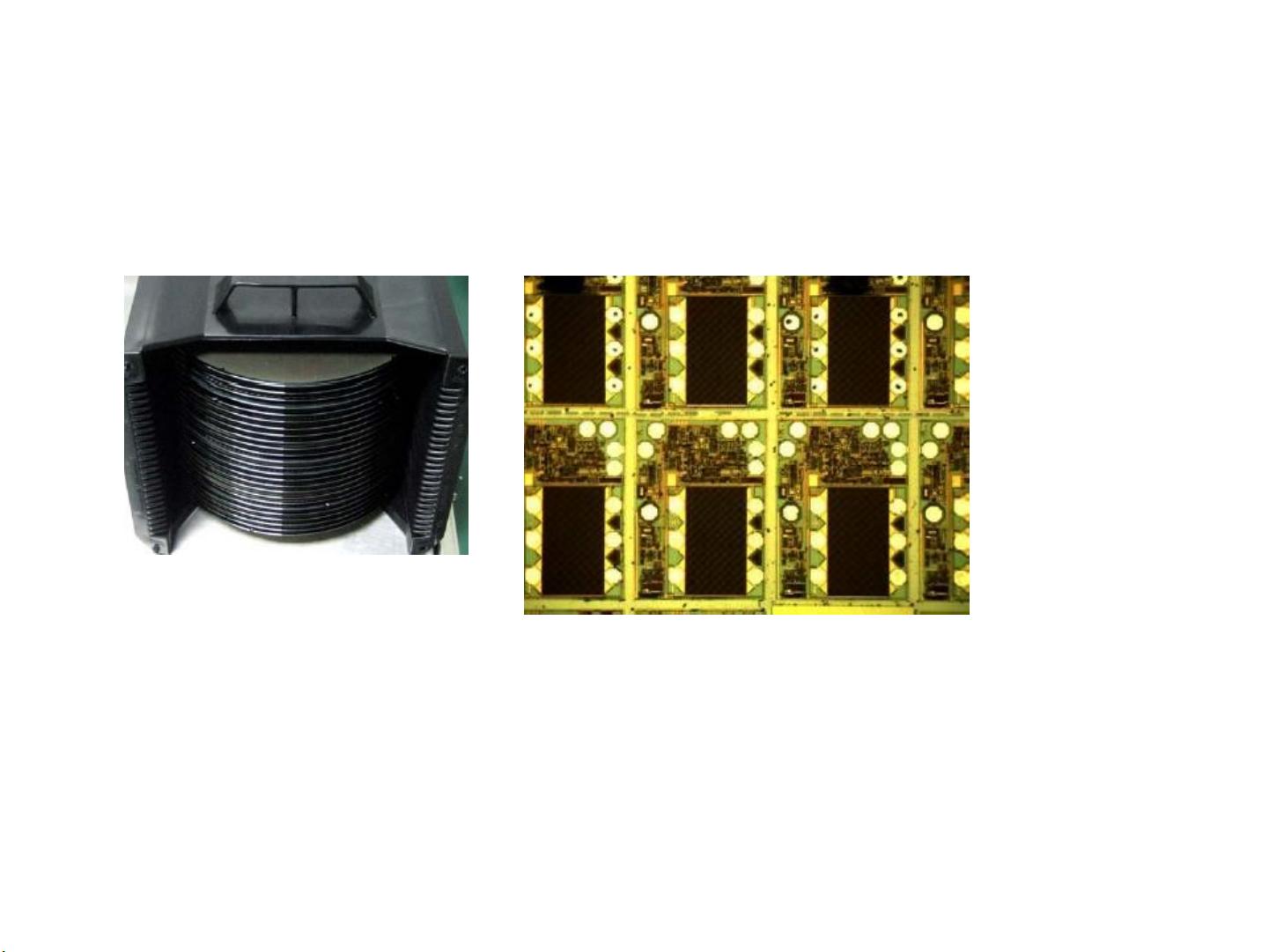

2. **晶圆制造(Wafer Fab)**:经过光刻、蚀刻等精密工艺,在硅片上制作出多个微小的集成电路单元,即die。

3. **晶圆测试(Wafer Probe)**:检查die的质量,确保每个芯片符合规格要求。

4. **封装测试(Assembly & Test)**:将合格的die与框架和塑封料结合起来,形成完整的封装,并进行电气性能测试。

5. **封装类型**:

- **按封装材料划分**:主要有金属封装、陶瓷封装和塑料封装。金属封装主要应用于军用或航空航天领域,因其稳定性高但成本高昂;陶瓷封装适合军事应用,但商业上较少见;塑料封装广泛用于消费电子产品,因成本低、工艺简单且可靠性高,市场占有率大。

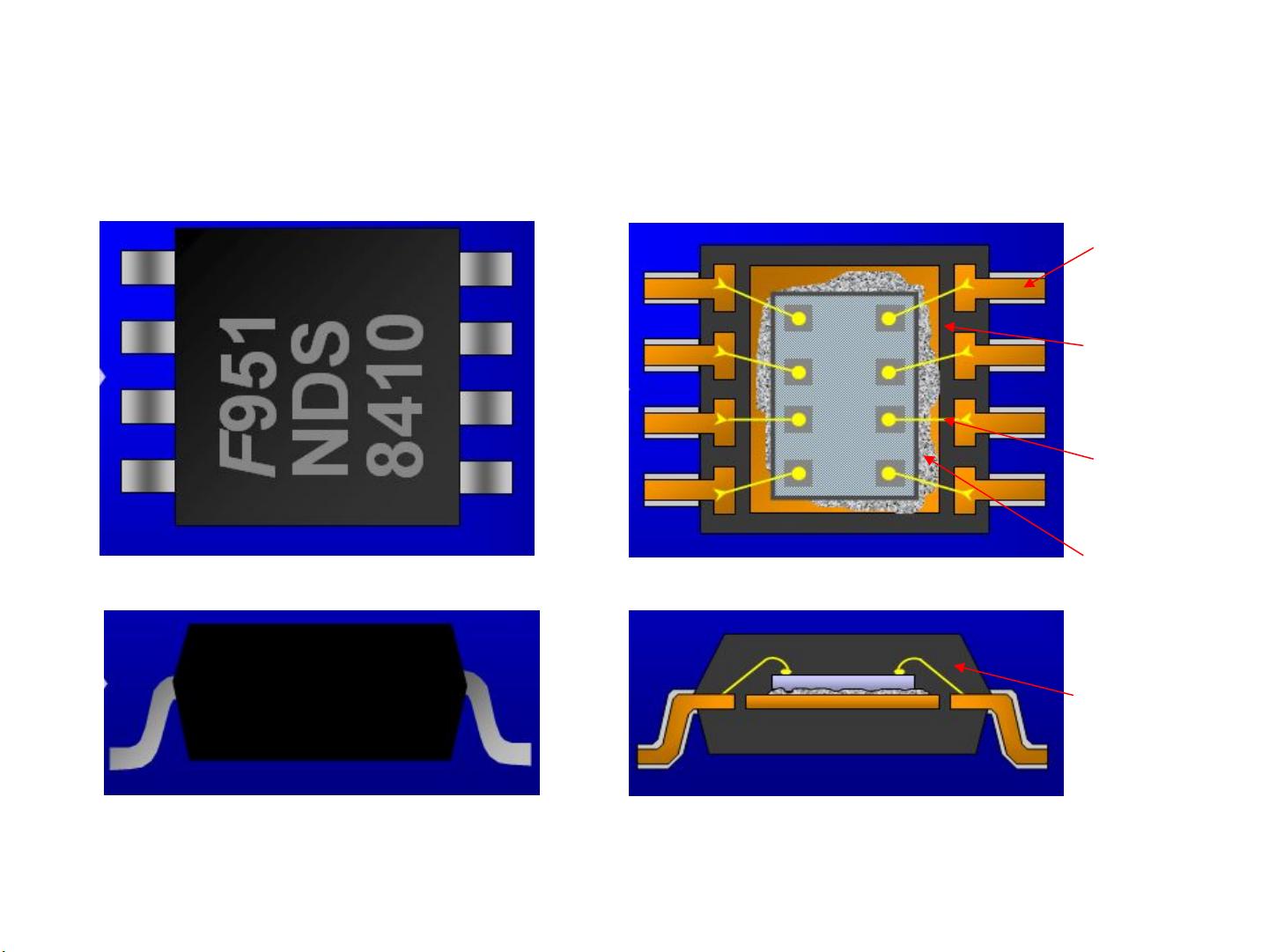

- **按连接方式划分**:有PTH(通孔式)和SMT(表面贴装式)。SMT已成为主流,因为它可以实现更小的体积和更高的密度。

6. **常见封装形式**:

- SOT(Small Outline Transistor):小型外形封装,适用于小型设备。

- SOIC(Small Outline Integrated Circuit):小外形集成电路,适合高密度应用。

- TSSOP(Thinned Small Shrink Outline Package):薄小外形封装,进一步缩小尺寸。

- QFP(Quad Flat Package):四方引脚扁平封装,提供更多的引脚数。

- BGA(Ball Grid Array):球栅阵列封装,通过球形焊盘与PCB板连接,提高密度和稳定性。

- CSP(Chip Scale Package):采用FlipChip技术和裸片封装,达到芯片面积和封装面积接近1:1的理想比例,代表了最高级的封装技术。

7. **选择封装形式考虑**:封装效率(芯片面积与封装面积的比例)和引脚数是决定封装形式的关键因素。随着技术的发展,封装形式和工艺变得越来越高级和复杂,以适应不断增长的性能需求和小型化趋势。

IC封装工艺是一个多步骤、技术密集的过程,它决定了集成电路最终产品的性能、尺寸和成本,对现代电子设备的性能和市场竞争力有着深远影响。