FPGA实验平台探索:Nexys4DDR与IP核应用

需积分: 0 81 浏览量

更新于2024-07-01

收藏 1.28MB PDF 举报

"实验07_FPGA实验平台及IP核使用 (1)1 - FPGA开发教程,介绍Nexys4DDR开发板,讲解原理图,使用Vivado和IP核"

在本次实验中,我们将深入探讨FPGA(Field-Programmable Gate Array)开发过程,特别是围绕Nexys4DDR实验平台和IP核的使用。实验的目标是让学习者能够熟练查看和理解FPGA开发的各个环节,掌握使用IP核进行电路设计的方法。

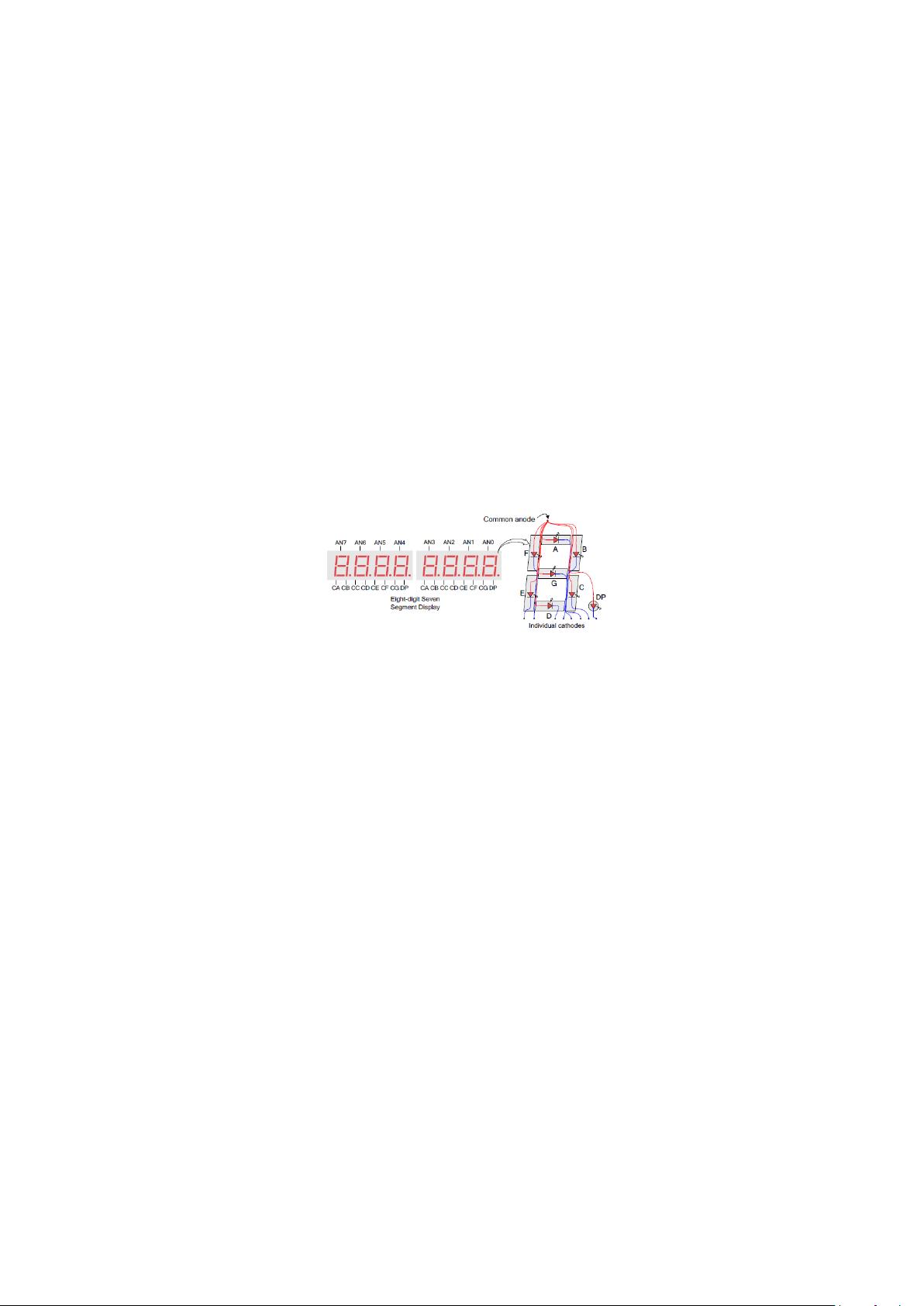

首先,Nexys4DDR开发板是一个强大的FPGA实验工具,它基于Xilinx的XC7A100TCSG324C-1 FPGA芯片,提供了丰富的外设,包括开关、按键、LED灯、数码管、PMOD接口以及多种通用接口如USB、RJ45、VGA等。这款开发板特别适合进行数字逻辑实验,构建嵌入式系统,甚至可以运行操作系统。

实验步骤中,Step1介绍了Nexys4DDR开发板的硬件特性。开发板上的外设如开关、按键、LED等都有明确的FPGA管脚对应,方便初学者快速上手。例如,我们之前已经通过开关控制LED灯的逻辑电路来熟悉这些基本操作。接下来,Step2将通过开发板的原理图进一步解释这些外设的工作原理和连接方式,以便于设计更复杂的电路。

在FPGA开发过程中,Vivado是一个重要的工具,它是Xilinx提供的集成设计环境,用于创建、仿真和实现FPGA项目。通过Vivado,我们可以编写Verilog代码来描述电路逻辑,并进行综合和布局布线,最终生成可烧录到FPGA的位流文件。

IP核,即 Intellectual Property Core,是预先设计好的功能模块,可以被重复使用在不同的设计中。在实验中,学习者将了解到如何利用IP核快速构建电路,比如时钟管理、接口控制器等,大大提高了设计效率和质量。

在电路设计和验证阶段,除了Vivado,我们还可以使用Logisim进行逻辑电路的模拟,以便在实际烧录前检查设计的正确性。此外,vlab.ustc.edu.cn可能是一个在线的实验平台,提供远程访问和协作功能,便于学习者进行实验和交流。

通过本实验,学习者不仅会掌握FPGA开发的基本技能,如Verilog编程、电路仿真和硬件验证,还将深入理解FPGA开发的流程,包括IP核的选用和配置。这将为后续的高级FPGA设计打下坚实基础。

2021-10-01 上传

2022-09-23 上传

219 浏览量

179 浏览量

162 浏览量

2010-03-10 上传

萌新小白爱学习

- 粉丝: 25

- 资源: 311

最新资源

- IA-32 Assembly Language

- DOS下常用网络相关命令解释

- GIS新引擎——“真图”数据解决方案.pdf

- 嵌入式Linux设备驱动开发.pdf

- JPA入门_PDF JPA

- 计算机网络技术 计算机网络技术

- 计算机通信技术计算机通信技术

- 初学者编程学习的文章

- BS EN 71-1-2005(+A4-2007)

- 消灭压力的高效工作方法

- 《Modeling Our World》中文版本

- Linux 上的GNOME 2.2 桌面用户指南.pdf

- Linux 系统上的GNOME 2.2 桌面管理指南.pdf

- 生化要点把一些生化要点都总结

- Linux内核完全注释-1.9.5.pdf

- 新版设计模式手册[C#]