定点原码一名乘法器设计详解

版权申诉

"计算机组成原理课程设计定点原码一名乘法器的设计"

计算机组成原理是一门深入理解计算机内部工作原理的学科,而定点原码一名乘法器是该领域中的一个重要概念。定点表示法是指数值的小数点位置固定不变,通常在二进制数的最右边。原码则是直接使用二进制表示数值,包括正负号。乘法器则是执行两个数相乘操作的硬件单元。

在这个课程设计中,学生需要设计一个能处理定点原码的乘法器,其工作原理基于传统的乘法规则。对于原码一名乘法,乘积的符号由两个乘数的符号位异或得到,数值部分则是两个绝对值的乘积。例如,如果X=0000,Y=1100,那么X*Y的计算过程会涉及到逐位判断乘数Y的每一位是否为1,根据判断结果决定是否将被乘数X左移一位并累加到部分积中。

设计中涉及的主要模块包括:

1. **乘数寄存器**:存储乘数,会在每次运算中按位右移,其最低位用于决定是否从被乘数寄存器取值。

2. **被乘数寄存器**:存储被乘数,通常保持不变,但其值会根据计算过程中的移位操作影响部分积。

3. **移位电路**:根据计数器的控制信号,将部分积和乘数按指定位数进行左移。

4. **控制器**:控制整个运算流程,包括何时移位、何时加法、何时更新部分积等。

5. **部分积寄存器**:保存每次相加并移位后得到的部分积,最终组合成完整的乘积。

6. **加法器(ALU)**:执行加法操作,通常在每次乘数的某位为1时,将被乘数左移一位后与当前部分积相加。

7. **计数器**:记录移位次数,当所有乘数位都处理完后,停止运算。

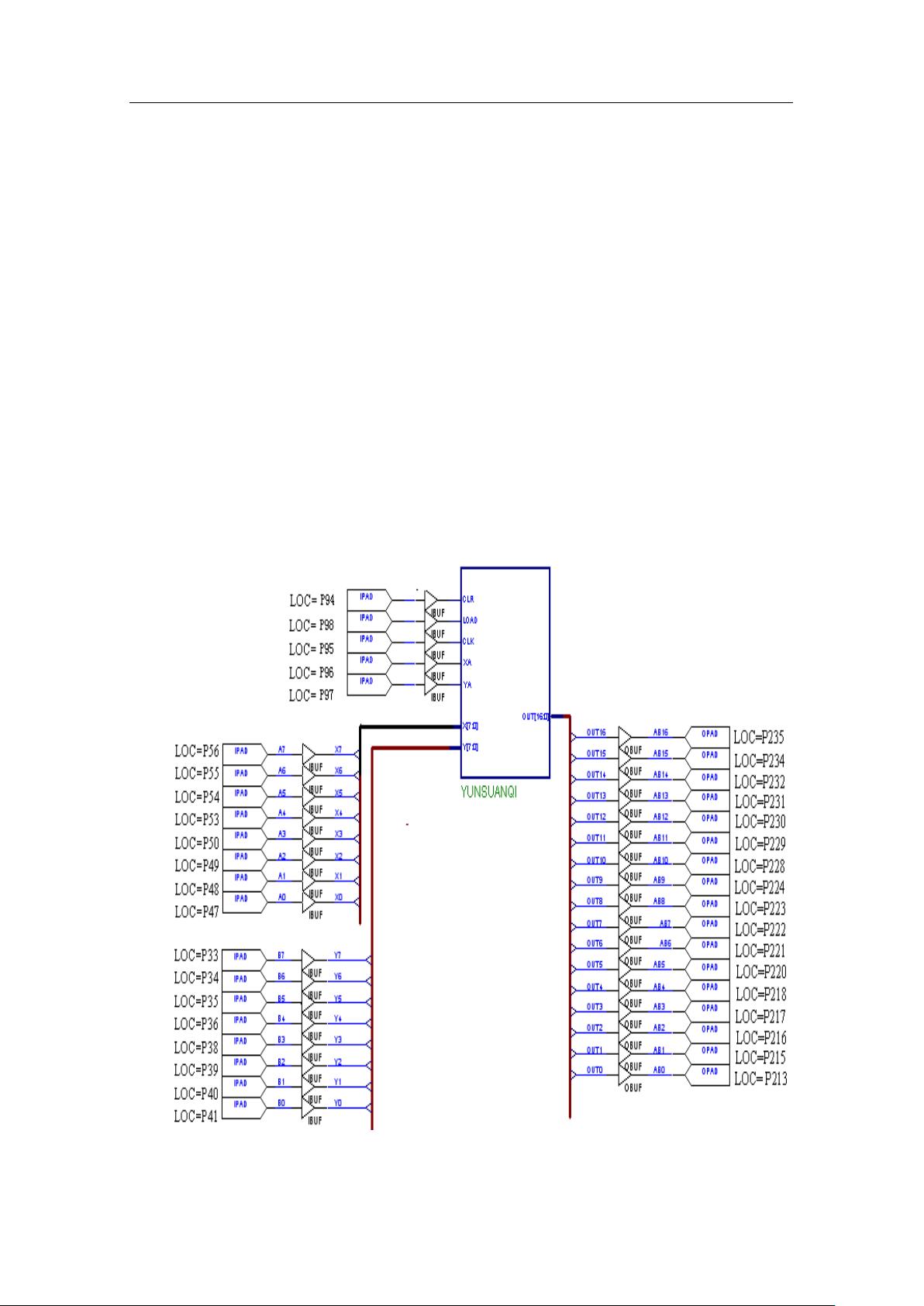

设计环境可能包括硬件平台,如FPGA(Field-Programmable Gate Array)或微处理器开发板,以及相应的软件工具,如硬件描述语言(如VHDL或Verilog)用于编写设计代码,仿真工具进行设计验证,以及编程下载工具将设计烧录到硬件设备中进行实际测试。

在硬件测试阶段,学生需要将编写的代码下载到硬件平台上,通过输入特定的测试用例,观察硬件实现的乘法器是否能正确输出预期的乘积。测试结果的分析可以帮助识别潜在问题并进行优化。

通过这样的课程设计,学生不仅可以深入理解计算机组成原理中的乘法运算,还能锻炼动手能力和系统设计思维,为未来在硬件设计和计算机系统开发领域的工作奠定基础。

2023-05-07 上传

点击了解资源详情

2011-01-03 上传

文档优选

- 粉丝: 95

- 资源: 1万+

最新资源

- 火炬连体网络在MNIST的2D嵌入实现示例

- Angular插件增强Application Insights JavaScript SDK功能

- 实时三维重建:InfiniTAM的ros驱动应用

- Spring与Mybatis整合的配置与实践

- Vozy前端技术测试深入体验与模板参考

- React应用实现语音转文字功能介绍

- PHPMailer-6.6.4: PHP邮件收发类库的详细介绍

- Felineboard:为猫主人设计的交互式仪表板

- PGRFileManager:功能强大的开源Ajax文件管理器

- Pytest-Html定制测试报告与源代码封装教程

- Angular开发与部署指南:从创建到测试

- BASIC-BINARY-IPC系统:进程间通信的非阻塞接口

- LTK3D: Common Lisp中的基础3D图形实现

- Timer-Counter-Lister:官方源代码及更新发布

- Galaxia REST API:面向地球问题的解决方案

- Node.js模块:随机动物实例教程与源码解析