17

www.ti.com/LVDS

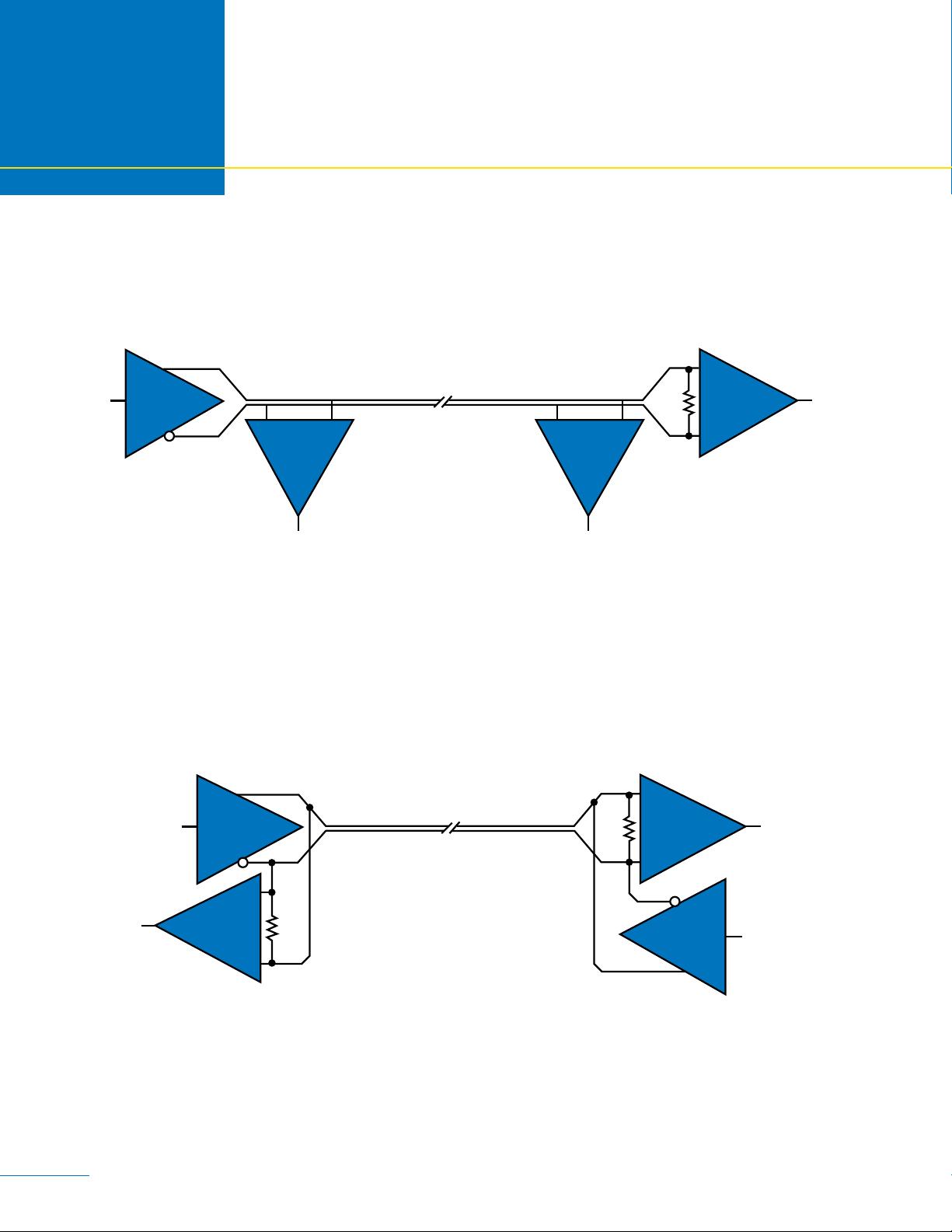

Physical connection of multiple drivers and receivers to a common signal bus presents unique challenges to successful

multidrop-topology designs. e major challenge that system designers encounter are the impedance discontinuities that

device loading and device connections (stubs) introduce on the common bus. Matching the impedance of the loaded bus

and using signal drivers with controlled signal edges are the keys to error-free signal transmissions in multipoint topologies.

Two versions of LVDS have been optimized for multipoint: Bus LVDS (B-LVDS) and Multipoint LVDS (M-LVDS).

B-LVDS shares many of the characteristics of LVDS but has much higher current drive (10 mA typical) and controlled

(slower) edge rates. B-LVDS is designed specically for driving multiple loads and in a well-designed backplane can support

up to 32 loads. B-LVDS-controlled edge rates help reduce reections in multidrop congurations with multiple loads and

associated stubs. e slower edges limit B-LVDS to slower data rates, typically below 1 Gbps.

e growth of B-LVDS in multidrop applications prompted the creation of an industry standard for an optimized version

of LVDS intended for such networks. National Semiconductor co-authored the standard that became TIA/EIA-899 and the

technology Multipoint LVDS (M-LVDS). M-LVDS includes all of the desirable attributes for multidrop including increased

drive, slow controlled edges, tighter input thresholds, and a wider common mode. M-LVDS is capable of driving 32 loads at

speeds up to 250 Mbps.

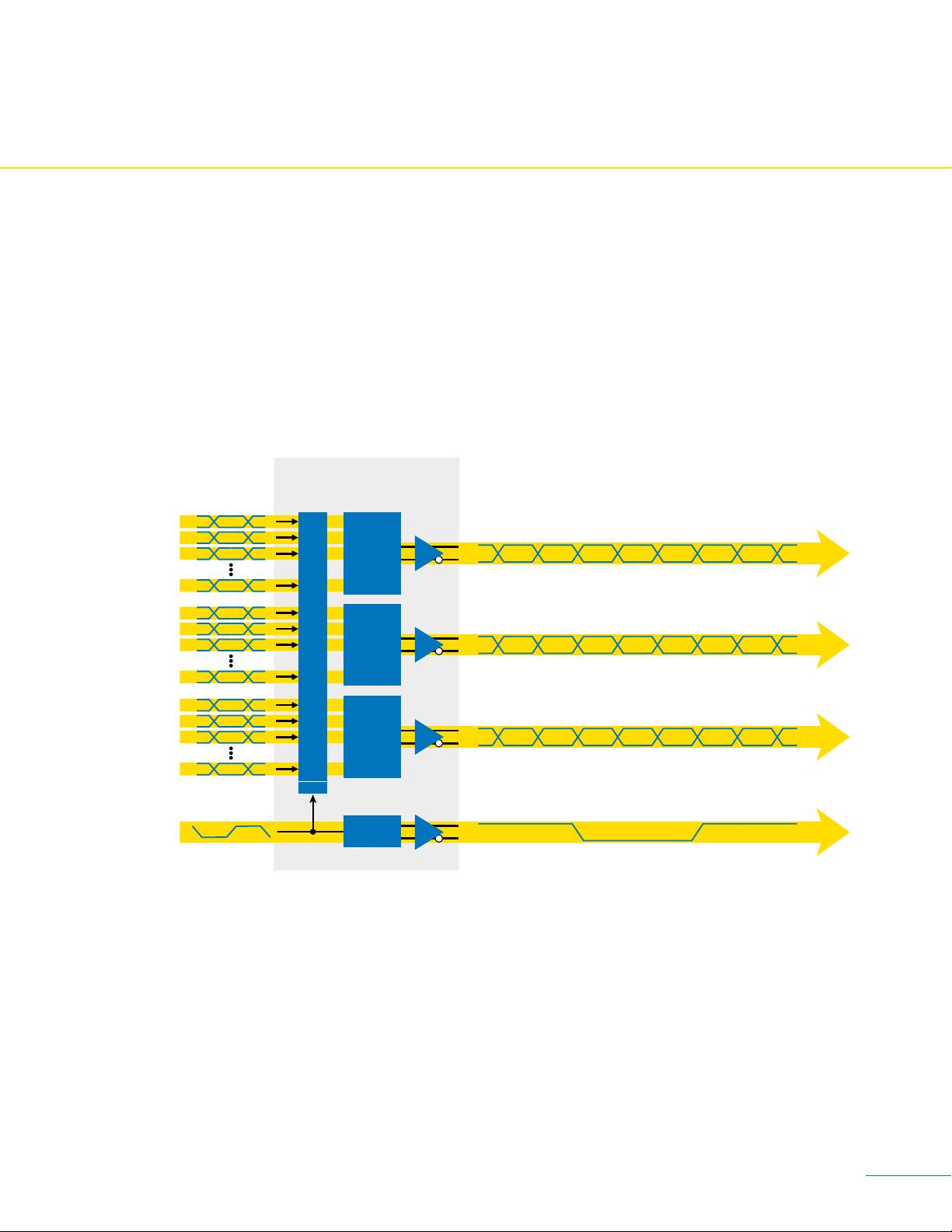

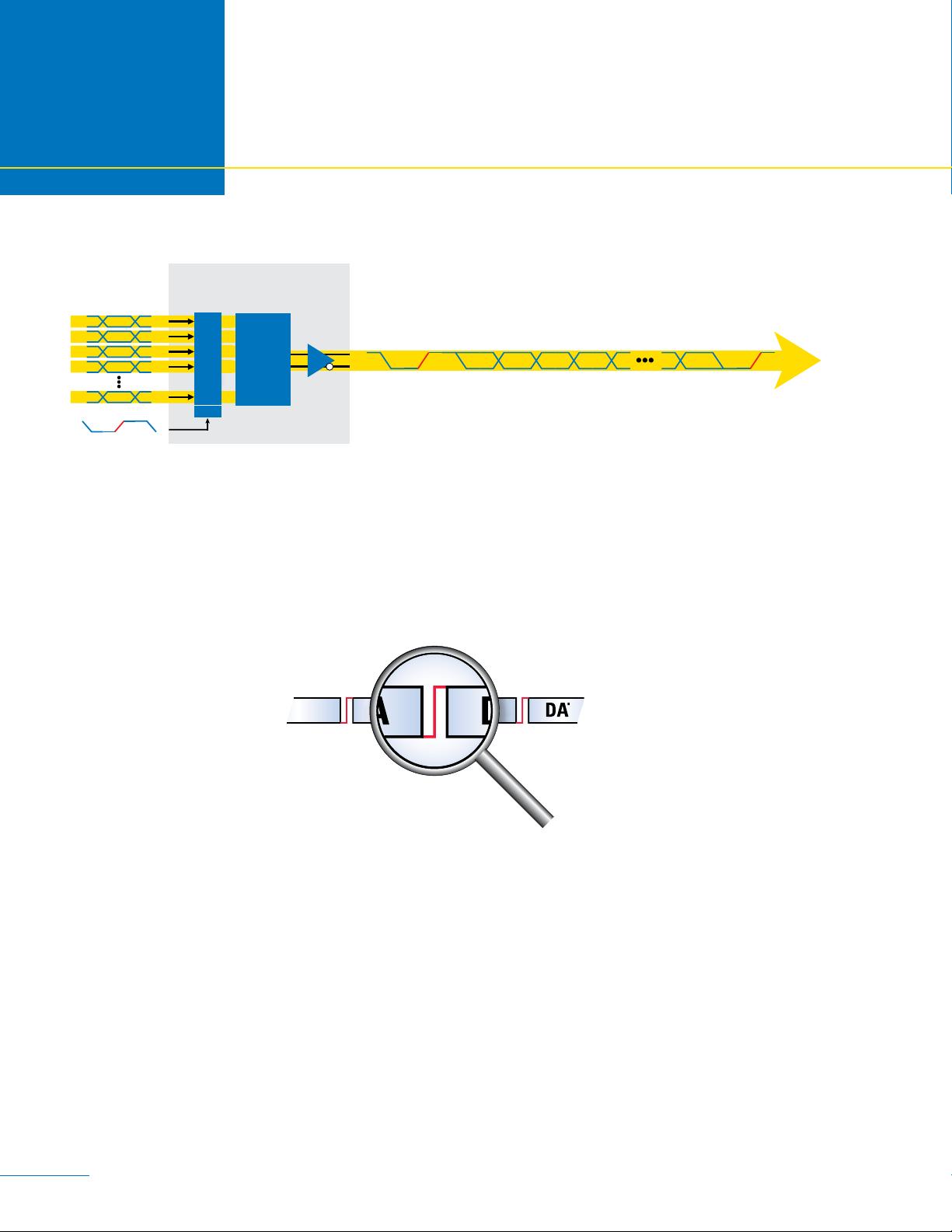

2.3 SerDes Architectures

Two obvious ways to add bandwidth are to either increase the bus speed or add parallel channels. Prior to the advent of

high-speed interface, the latter approach was often selected, resulting in very wide Low-Voltage Transistor-to-Transistor

Logic (LVTTL) buses and backplanes. e technique of combining slower LVTTL signals into a single-bit stream (serial-

izer), transporting the data at high speed and then redistributing at the receiver (deserializer), is very common and often

referred to as Serializer/Deserializer (SerDes). e dierent SerDes architectures and advantages of each are covered in the

SerDes Architectures Section on page 19.

2.4 Mixing Signaling Technologies

It is quite common for hardware platforms to have multiple signaling requirements for clocks, data, and control signals.

In modular systems, card-to-card or box-to-box communication may involve dierent vendors and technologies. For

these reasons, LVDS, LVPECL, and CML often coexist in the same platform, and translation between dierent signaling

technologies is a necessary component of system design.

One approach to simplify translation is to AC couple the two networks using capacitors in each of the dierential channels.

is technique eliminates DC osets and threshold dierences, however AC coupling requires DC-balanced data. For

non-DC-balanced data, various termination networks allow translation between technologies. For a full discussion on

translation networks, see Termination and Translation, page 31.

2.5 Selecting an Interface Technology

e selection of an interface device or technology is an important one. Error-free and reliable signal transmission is a critical

component of many systems. e rst decisions are often the topology: Will the network be point-to-point or multidrop?

Will SerDes be required? Bandwidth, power, and jitter budgets then need to be considered.

LVDS is the most common high-speed interface and has the dual advantages of low power and wide common mode.

LVPECL generally uses additional power but supports very high data rates with excellent jitter. CML devices oer similar

performance to LVPECL and have the advantage of a simple and usually integrated termination.

Network Topology