优化8输入CMOS与非门设计:掌握大扇入电路技巧

需积分: 50 57 浏览量

更新于2024-09-12

2

收藏 846KB DOCX 举报

本资源主要探讨了CMOS八输入与非门的课程设计,重点在于通过性能优化来掌握大扇入组合逻辑电路的设计策略。实验目标包括熟悉8输入与非门的性能优化方法以及掌握HSPICE等电子设计自动化(EDA)软件的运用。

实验原理部分详细介绍了针对大扇入设计的技术手段,如调整晶体管尺寸、逐级增大、重新安排输入和逻辑结构的重组。其中,传播延时与输入模式的关系被强调,特别是当涉及输出由低至高翻转的情况,选择特定输入模式(如全1到1的变化)来简化模拟分析。对于输出由高到低的情况,由于内部节点电容的影响,延时计算更为复杂,此时需考虑节点的初始状态。

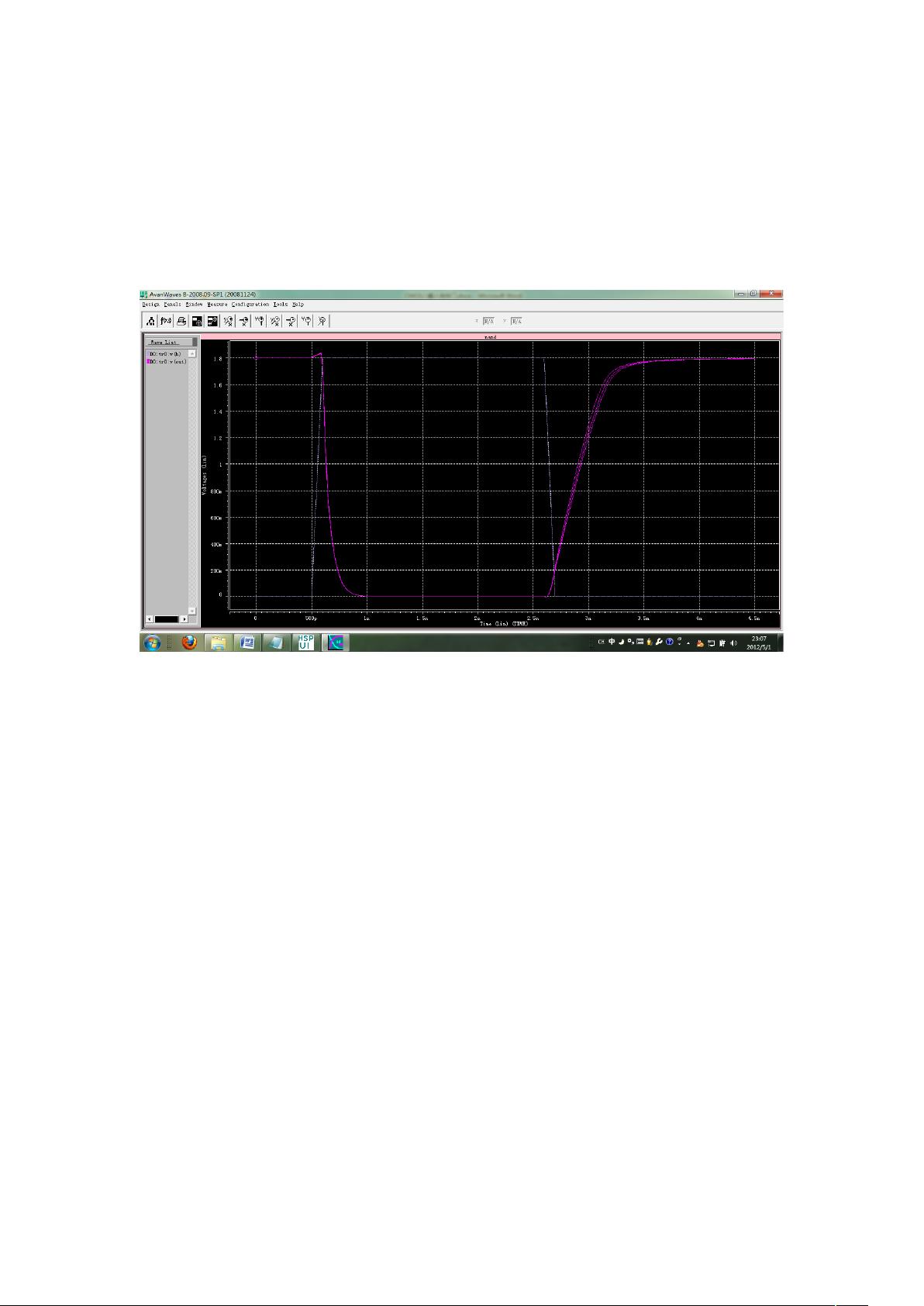

在实验内容方面,使用的是HSPICE C-2009.09软件和MM180_LVT18_V113工艺库,设定的参考反相器比例为Wp/Wn=2/1,并确定了八输入与非门的Wp/Wn=2/8,具体参数如Wp/L=2,L=0.18um,Wn/L=8。实验中,首先验证了当负载电容主要是门本身的电容时,晶体管尺寸调整对传播延时不产生影响。通过分别设置Wp/L为2、3、4来模拟,代码展示了如何在HSPICE中实现这一部分的仿真。

此外,资源还涵盖了其他设计技术的验证,如针对扇出为主的负载,放大晶体管尺寸可能会影响传播延时。整个过程旨在通过实践操作,使学生深入理解并掌握CMOS电路设计中的优化技巧,以及如何利用HSPICE这样的工具进行有效的性能评估。

227 浏览量

118 浏览量

631 浏览量

2553 浏览量

点击了解资源详情

238 浏览量

991 浏览量

点击了解资源详情

237 浏览量

wy0330

- 粉丝: 0

最新资源

- 初学者入门必备!Visual C++开发的连连看小程序

- C#实现SqlServer分页存储过程示例分析

- 西门子工业网络通信例程解读与实践

- JavaScript实现表格变色与选中效果指南

- MVP与Retrofit2.0相结合的登录示例教程

- MFC实现透明泡泡效果与文件操作教程

- 探索Delphi ERP框架的核心功能与应用案例

- 爱尔兰COVID-19案例数据分析与可视化

- 提升效率的三维石头制作插件

- 人脸C++识别系统实现:源码与测试包

- MishMash Hackathon:Python编程马拉松盛事

- JavaScript Switch语句练习指南:简洁注释详解

- C语言实现的通讯录管理系统设计教程

- ASP.net实现用户登录注册功能模块详解

- 吉时利2000数据读取与分析教程

- 钻石画软件:从设计到生产的高效解决方案