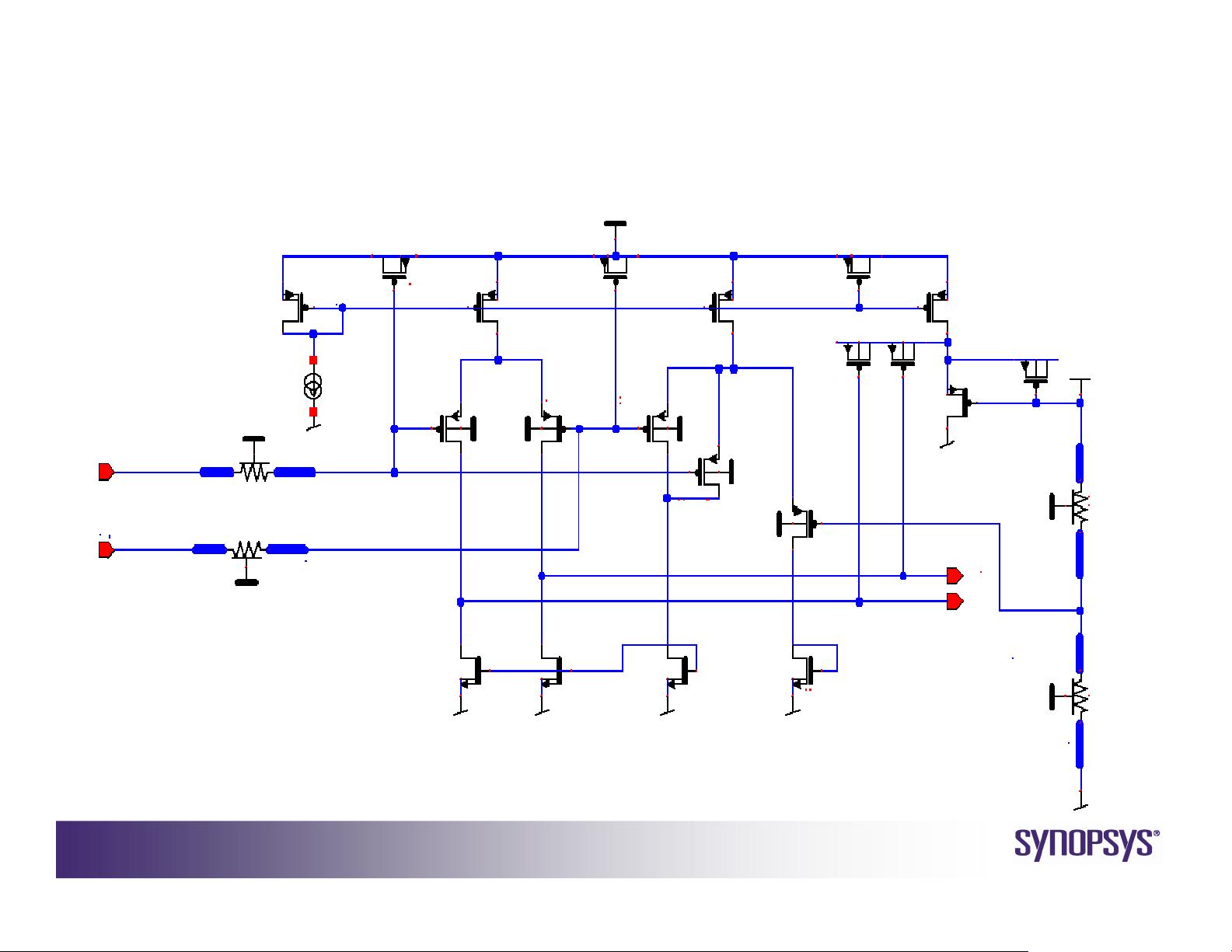

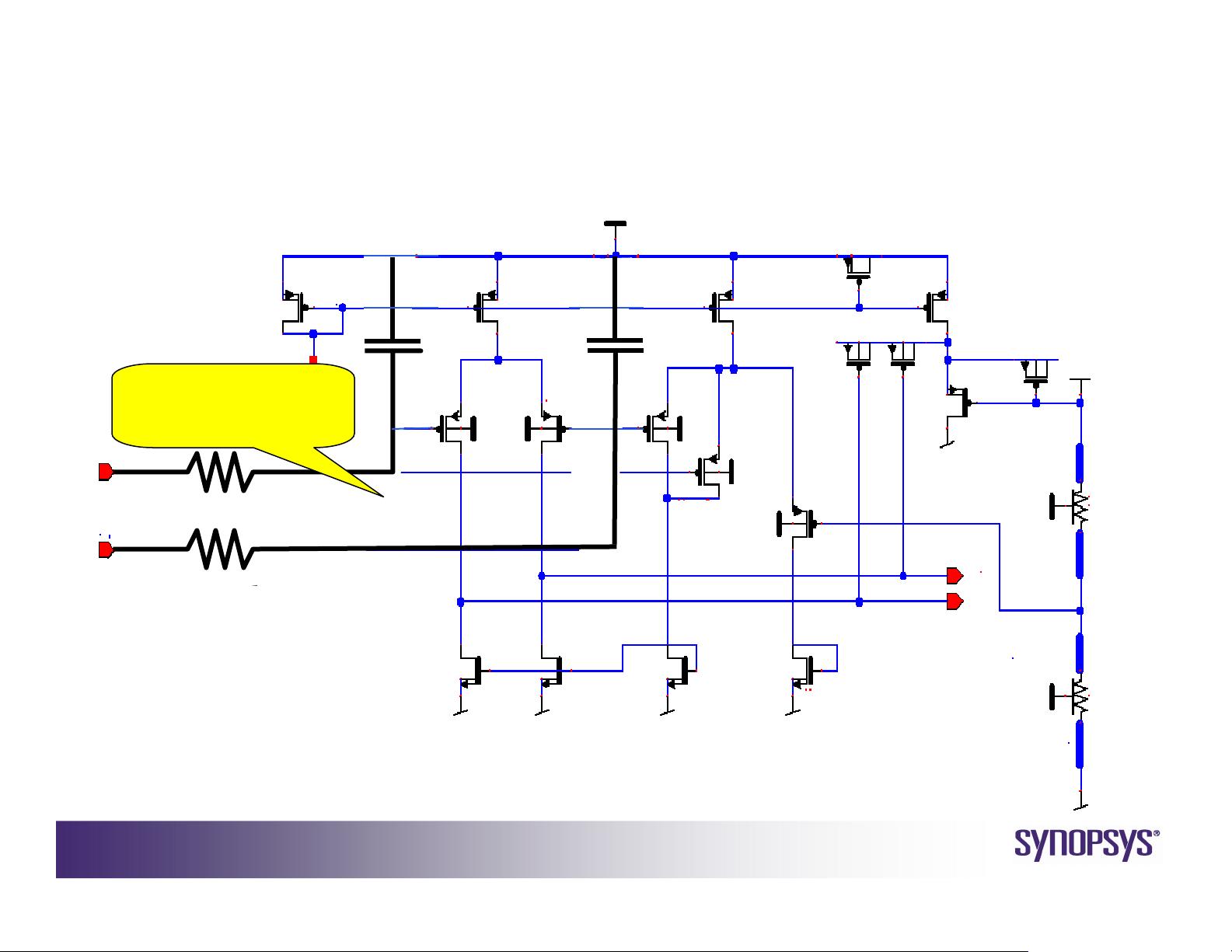

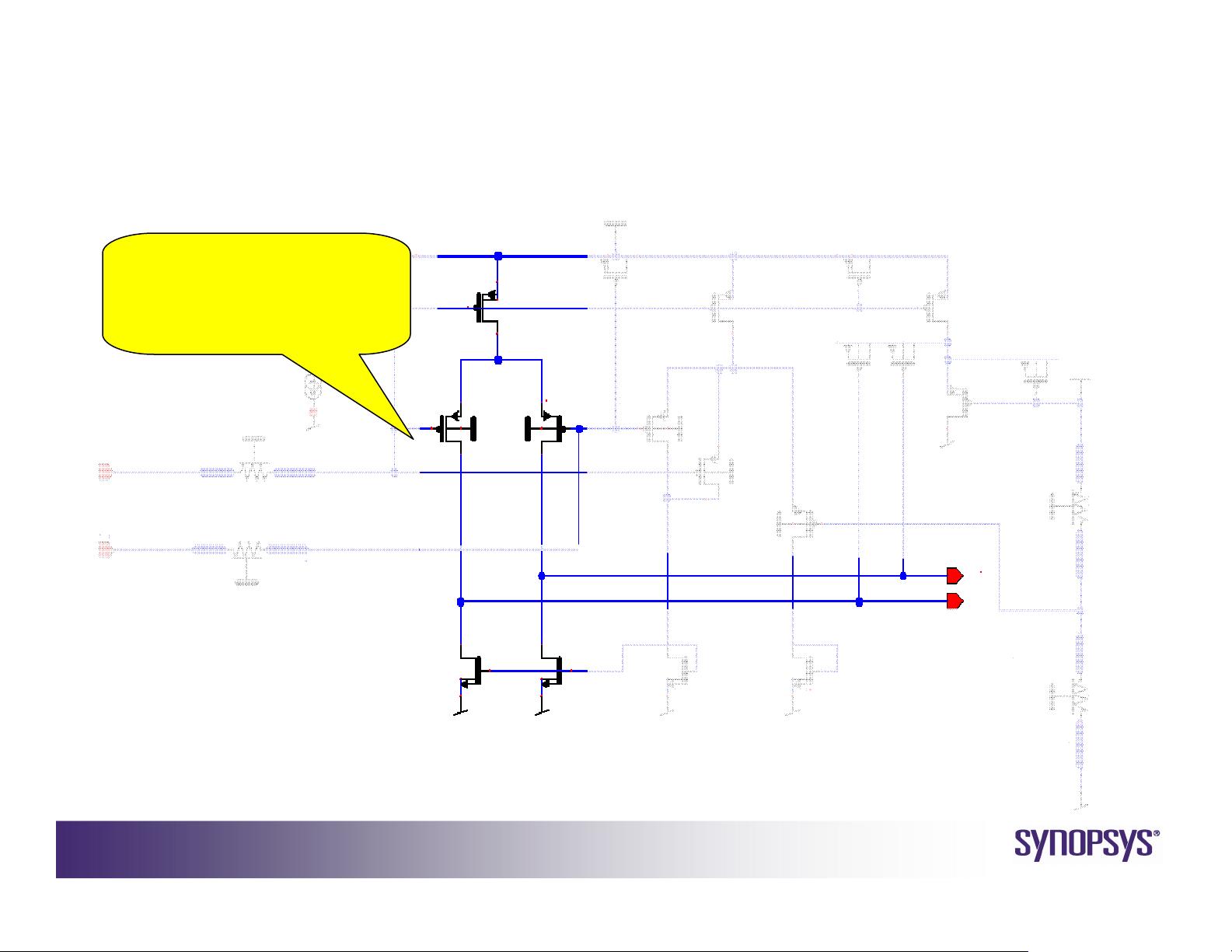

"Analog Design at 65 nm" 是一份关于在65纳米工艺下进行模拟设计的技术报告,由Bob Lefferts和Navraj Nandra在SNUG Israel 2007会议上提出。报告主要关注了在亚波长技术中的模拟与数字设计差异、混合信号设计的分区策略、一个具体的混合信号设计实例——周期校正器、模拟设计中的关键变异性源以及65纳米节点的模拟设计趋势。 1. 模拟与数字设计在亚波长技术的对比: 在亚微米或更小的工艺节点(如65纳米)中,模拟设计与数字设计面临着不同的挑战。数字设计通常可以受益于更小的晶体管尺寸和更高的集成度,而模拟设计则需要处理噪声、精度和稳定性的问题。随着工艺尺寸的缩小,模拟电路的性能可能会受到诸如短通道效应、线性区的减少等影响。 2. 设计分区(混合信号设计): 混合信号设计是将模拟和数字电路集成在同一芯片上的方法。设计分区是解决这种复杂集成的关键,它涉及到如何有效地分配模拟和数字部分,以实现最佳性能和可制造性。有效的分区可以帮助减少设计的复杂性,提高电路的稳定性和可预测性。 3. 混合信号设计示例:周期校正器: 周期校正器是一种用于确保时钟信号具有恒定占空比的电路,这对于高速通信和数据处理系统至关重要。在65纳米工艺下,设计这样的电路需要考虑工艺变量的影响,并进行精确的建模和仿真,以确保其在各种条件下的工作性能。 4. 关键的变异性源: 报告列举了影响模拟设计的几个关键变异性源,包括: - STI(浅沟槽隔离):会影响晶体管的阈值电压。 - WP(晶界):可能导致电流密度不均匀。 - CS(掺杂浓度剖面形状):可能影响器件的电气特性。 - OPC/PSM(光学掩模补偿/相移掩模):对光刻过程中的分辨率和精度有影响。 - NBTI(负栅极偏压退化):长期工作后导致晶体管性能下降。 - HCI(热点载流子注入):高温操作可能导致器件性能退化。 5. 65纳米节点的模拟设计趋势: 在65纳米工艺中,模拟设计趋势包括更低的噪声要求、更严格的抖动控制(例如在低抖动PCI Express PHY的设计中),以及通过优化设计以提高USB 2.0 PHY的良率。"Yield by design"的概念强调了在设计阶段就考虑制造可预测性和可制造性,以提高最终产品的成功率。 这份报告提供了深入的洞察,对于理解65纳米技术下模拟电路设计的挑战和应对策略具有重要意义,同时也展示了在先进工艺节点中如何实现模拟设计的可靠性和效率。

剩余67页未读,继续阅读

- 粉丝: 0

- 资源: 2

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- zlib-1.2.12压缩包解析与技术要点

- 微信小程序滑动选项卡源码模版发布

- Unity虚拟人物唇同步插件Oculus Lipsync介绍

- Nginx 1.18.0版本WinSW自动安装与管理指南

- Java Swing和JDBC实现的ATM系统源码解析

- 掌握Spark Streaming与Maven集成的分布式大数据处理

- 深入学习推荐系统:教程、案例与项目实践

- Web开发者必备的取色工具软件介绍

- C语言实现李春葆数据结构实验程序

- 超市管理系统开发:asp+SQL Server 2005实战

- Redis伪集群搭建教程与实践

- 掌握网络活动细节:Wireshark v3.6.3网络嗅探工具详解

- 全面掌握美赛:建模、分析与编程实现教程

- Java图书馆系统完整项目源码及SQL文件解析

- PCtoLCD2002软件:高效图片和字符取模转换

- Java开发的体育赛事在线购票系统源码分析

信息提交成功

信息提交成功