UVM 1.2 技术参考:通用验证方法

需积分: 5 128 浏览量

更新于2024-07-04

1

收藏 9.03MB PDF 举报

"Universal Verification Methodology (UVM) 1.2 Class Reference 是一份由Accellera Systems Initiative在2014年发布的文档,详细介绍了UVM 1.2版本的类参考信息,主要涉及SystemVerilog语言的验证方法学。这份文档旨在为使用UVM进行硬件验证的工程师提供指南,内容涵盖了UVM的核心组件和接口,以及如何构建可复用的验证环境。"

正文:

Universal Verification Methodology (UVM) 是一种基于SystemVerilog的行业标准验证方法学,它提供了一套用于系统级验证的类库、框架和指导原则。UVM 1.2是该方法学的一个关键版本,它包含了对之前版本的改进和增强,以满足更高效、更灵活的验证需求。

在UVM 1.2中,主要的知识点包括以下几个方面:

1. **基础组件**:UVM的基础组件包括代理(agent)、序列器(sequencer)、驱动(driver)、接收器(monitor)和环境(environment)。这些组件协同工作,实现对设计的激励生成、传输、响应收集和结果分析。

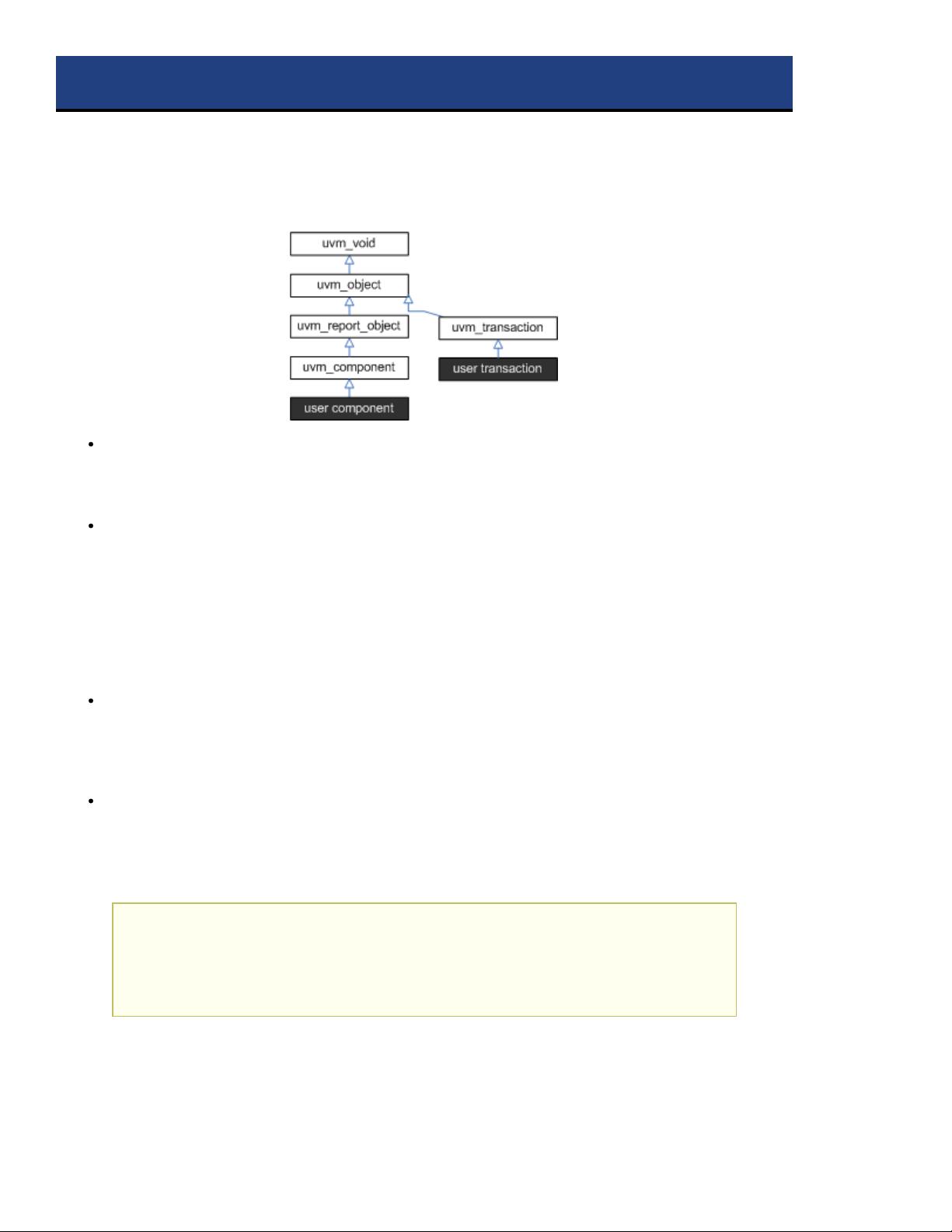

2. **类层次结构**:UVM的核心类如uvm_component、uvm_sequence_base、uvm_transaction等构成了一个丰富的继承层次结构,允许用户通过子类化来定制和扩展验证行为。

3. **通信机制**:UVM使用事件、队列和接口(如uvm_analysis_port)来实现组件间的通信。这使得验证组件能有效地协调工作,例如,驱动与接收器之间的数据传递,以及接收器向分析组件报告数据。

4. **配置和覆盖管理**:UVM提供了强大的配置管理机制,允许在运行时动态配置组件的属性。覆盖管理则支持度量验证覆盖率,确保验证的全面性。

5. **工厂和注册表**:UVM工厂负责实例化组件,而注册表则记录了所有已知的组件类型,便于查找和使用。

6. **随机化和约束**:UVM提供了基于SystemVerilog的随机化机制,使得激励生成可以根据预定义的约束进行随机化,提高了验证的覆盖率。

7. **事务级别模型(TLM)**:UVM支持事务级别模型,允许抽象化数据传输,使得验证组件可以独立于具体的数据结构和协议细节。

8. **宏和实用工具**:UVM提供了一系列便利的宏和函数,如`uvm_error`、`uvm_info`等,简化了错误处理和信息报告。

9. **可复用性和可扩展性**:UVM的设计原则鼓励模块化和可重用性,用户可以通过组合和扩展现成的UVM组件来快速搭建复杂的验证环境。

10. **一致性测试**:UVM还包含了一组一致性测试用例,用于验证用户自定义的UVM组件是否符合UVM规范,确保其正确集成到UVM环境中。

使用UVM 1.2 Class Reference,开发者能够深入理解每个类的功能、接口和用法,从而更加熟练地运用UVM进行系统级验证。不过,需要注意的是,尽管UVM提供了强大和灵活的验证工具,但使用过程中应遵循最佳实践,确保验证的有效性和可靠性。同时,由于Accellera不独立验证标准中的信息准确性,用户在实际应用时仍需谨慎评估和测试。

2018-08-06 上传

2019-04-11 上传

2017-09-08 上传

2022-11-08 上传

点击了解资源详情

点击了解资源详情

EdwardRen2012

- 粉丝: 0

- 资源: 4

最新资源

- The Next 700 Programming Languages

- 2009年上半年信息系统监理师上午题。

- 2009年上半年信息处理技术员上午题

- AT&T asm guide for newbie

- DSP开发板电路原理图之主图

- 管理软件的实施与销售

- The estimation of synergy or antagonism

- Measuring additive interaction using odds ratios

- 数据库课程设计126个经典题

- 【启动项目就是开机的时候系统会在前台或者后台运行的程序】

- 云母填充改性聚乙烯的初步研究

- 某高校学生学籍管理信息系统设计与开发

- 编程相关日语词汇(PDF格式)

- Ubuntu中文参考手册

- 计算机网络 第四版 习题答案 谢希仁

- J2ME手机游戏开发技术详解