理解与避免 FPGA 设计中的锁存器问题

"这篇文章主要介绍了FPGA中的锁存器,包括其工作原理和如何避免在设计中不自觉地使用锁存器。"

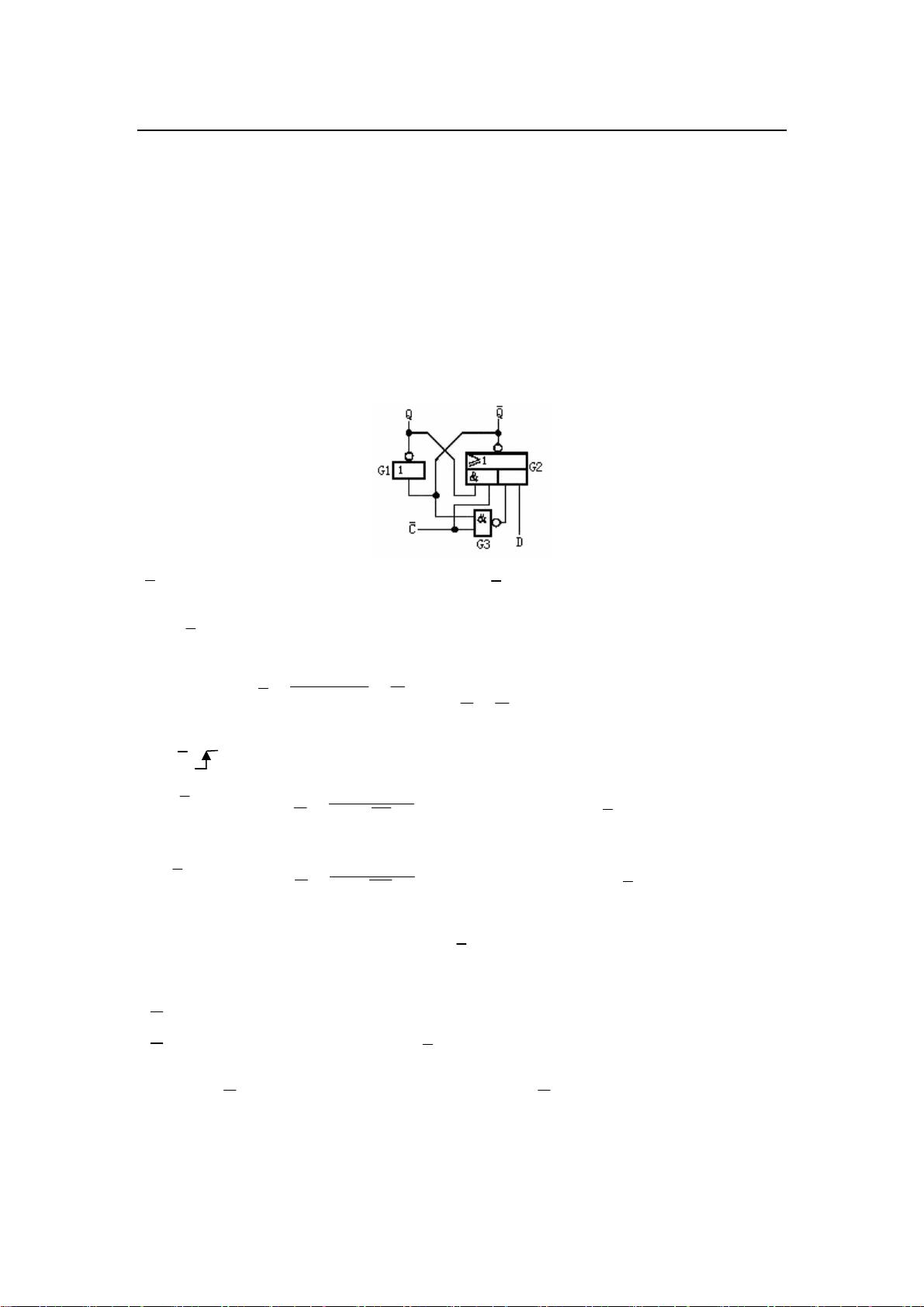

在FPGA设计中,锁存器(Latches)是一个重要的概念,但如果不正确使用,可能会导致时序问题和设计复杂性增加。锁存器与触发器不同,它通过电平信号而非时钟来控制数据的存储。当锁存控制信号(如C)为低时,锁存器允许输入信号(D)自由流动到输出(Q和Q),类似于一个缓冲器;而当C为高时,输入信号被“锁存”,输出保持之前的状态,不受输入信号的影响。

锁存器的工作原理可以通过简单的逻辑门电路来理解。在一个典型的锁存器电路中,有两个互补的输出Q和Q,以及一个数据输入D和一个控制输入C。当C为低时,输入D可以通过与门到达输出Q和Q,实现数据的透明传输;当C变为高时,与门被封锁,之前D的状态被“锁存”在输出端,即使D改变,输出Q和Q也不会受到影响,从而保持先前的数据。

设计者应尽量避免在FPGA设计中使用锁存器,因为它们可能引入非确定性的时序路径,这在高速数字设计中是非常不利的。通常,时钟同步的触发器被更优先选择,以确保数据在时钟边沿稳定且可预测地改变。然而,在某些特定情况下,如使用GTECHD锁存器或者在寄存器堆、内存、FIFO等结构中,锁存器的使用是允许的,但必须有详细的文档记录,并满足特定的时序要求。

为防止无意间在设计中创建锁存器,设计师需要注意编程语言的使用。例如,在Verilog中,if语句如果没有配对的else语句可能导致锁存器的产生,因为未被处理的条件会使得输出状态保持不确定。同样,在VHDL中,当使用when...others条件时,如果没有为所有其他情况分配默认值,也可能无意间创建了锁存器。

因此,使用设计检查工具对代码进行检查是非常必要的,可以检测出潜在的锁存器并提供改进建议。通过了解锁存器的工作原理和避免锁存器的策略,设计师能够更好地管理FPGA设计中的时序问题,确保设计的稳定性和可靠性。

2009-12-18 上传

2010-08-02 上传

2008-08-05 上传

2011-12-24 上传

2012-10-30 上传

2022-09-14 上传

2021-10-02 上传

2023-10-08 上传

2024-06-23 上传