DDR4无缓冲DIMM原始卡A设计规范详解

需积分: 49 86 浏览量

更新于2024-07-18

1

收藏 296KB PDF 举报

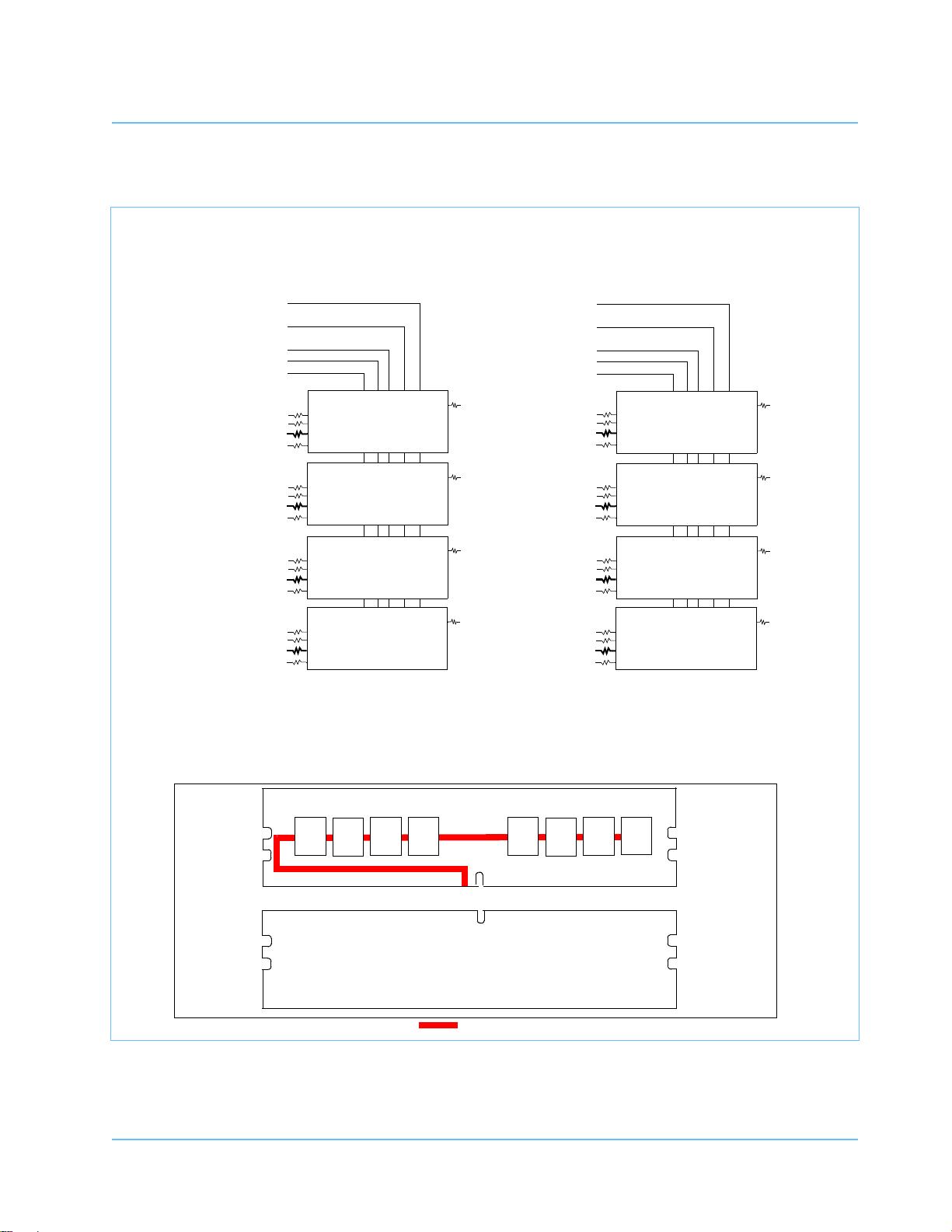

"DDR4 Unbuffered DIMM Raw Card A 设计规范是内存台式机DDR4单面板设计的关键指导文件,遵循JEDEC Standard No.21C的标准。该规范涵盖了不同版本的设计文件,如A0和A1,并提供了对应版本的电路板设计文件(.brd)和物料清单(.xlsx)。此设计规范旨在确保DIMM模块的兼容性和可靠性,同时也允许随着技术发展进行必要的更新。"

DDR4 Unbuffered DIMM Raw Card A的设计涉及多个方面:

1. **JEDEC标准**:DDR4内存设计严格遵循JEDEC设定的标准,这确保了不同厂商的内存组件能在同一平台上无缝工作。JEDEC Standard No.21C是针对DRAM模块的详细规格。

2. **模块配置**:DDR4内存模组(DIMM)使用了SDRAM芯片,其配置包括了最小和最大SDRAMDie数量、逻辑Rank和包内Rank的数量,以及行地址和列地址的位数。例如,对于2GB的模组,它由256Mbx64的2Gb芯片组成,使用8/8的Rank配置。

3. **Rank结构**:每个DIMM可以有1个或多个逻辑Rank和包内Rank,这取决于内存容量。逻辑Rank是内存控制器看到的独立内存单元,而包内Rank是在物理封装内的独立DRAM单元。在上述例子中,所有配置都只有一个Rank。

4. **地址映射**:地址线A16是最高的地址位,与RAS_n信号复用。这意味着地址线和控制信号的复用是DDR4设计中的一个重要考虑因素,以优化信号完整性和减少引脚数量。

5. **容量和组织**:内存模组的容量和内部组织与DRAM芯片的密度有关。例如,16GB的模组由2Gbx64的16Gb芯片构成,采用1Gbx8的组织结构,表示每个DRAM芯片有8个bank,每个bank有8位宽的数据路径。

6. **设计文件**:附带的设计文件如A0和A1版的.brd文件,是电路板布局的电子表示,用于指导实际的硬件制作。同时,.xlsx文件包含了物料清单,列出了所有必要的组件及其数量,是制造过程的重要参考。

7. **持续更新**:虽然规范文件反映了最新的设计文件,但可能会根据标准的澄清或更新进行调整。在这种情况下,设计文件本身可能不会立即更新,但规范会及时反映这些变化。

DDR4 Unbuffered DIMM Raw Card A的设计规范是一个全面的指南,它定义了从内存组件选择到物理布局的所有细节,以满足高性能、低功耗和高可靠性的要求,适用于台式机平台的内存系统。

392 浏览量

365 浏览量

点击了解资源详情

392 浏览量

365 浏览量

2021-09-02 上传

2021-09-02 上传

2021-10-01 上传

305 浏览量

中国永

- 粉丝: 5

- 资源: 11

最新资源

- CUDA9.0+cudnn7安装大礼包.zip

- 拖动滑块进行验证

- Docker零基础学习全套教程(含项目实战和源码)

- tarea-express-v1

- 网钛淘拍系统官方网下载v1.51

- 着作权法案例判决评析——计算机程序之保护

- uorhousepositions:简单的Powershell脚本可下载UOR房屋位置并创建地图文件

- multisetdiff:与 setdiff 类似,但 A 的任何重复元素在 B 中每次出现时仅被删除一次-matlab开发

- 愤怒的小鸟-阶段4:愤怒的小鸟-阶段4

- devopsproject1

- gcc内网离线安装包,CentOS7亲测可用

- ion-tools:工具和实用程序,使ION网络工作和使用ION DID变得轻松自如

- 工程建设项目管理体制

- RecommenderOnTf2:基于TensorFlow 2.3实现的推荐系统神经网络,主要关注模型构建,基本不包含数据预处理阶段

- LFO - Maker:用于构建不同 LFO 类型的系统-matlab开发

- diabetic-retinopathy:基于人眼图像的糖尿病性视网膜病变分类系统