DDR4无缓冲DIMM原始卡C设计规范详解

需积分: 29 110 浏览量

更新于2024-09-05

收藏 163KB PDF 举报

"DDR4 Unbuffered DIMM Raw Card C设计规范主要涵盖了JEDEC标准、模块配置、SDRAM配置以及支持的DRAM外形等关键信息。该规范是针对台式机DDR4内存的设计标准,适用于x16位接口,并提供了具体的设计文件和物料清单(BOM)。"

DDR4 Unbuffered DIMM(无缓冲双列直插内存模块)是根据JEDEC(固态技术协会)的标准进行设计的,标准号为JEDEC Standard No. 21C,版本为Release 26, Revision 1.10。这些规范确保了不同制造商生产的DDR4内存模块之间的兼容性和互换性。

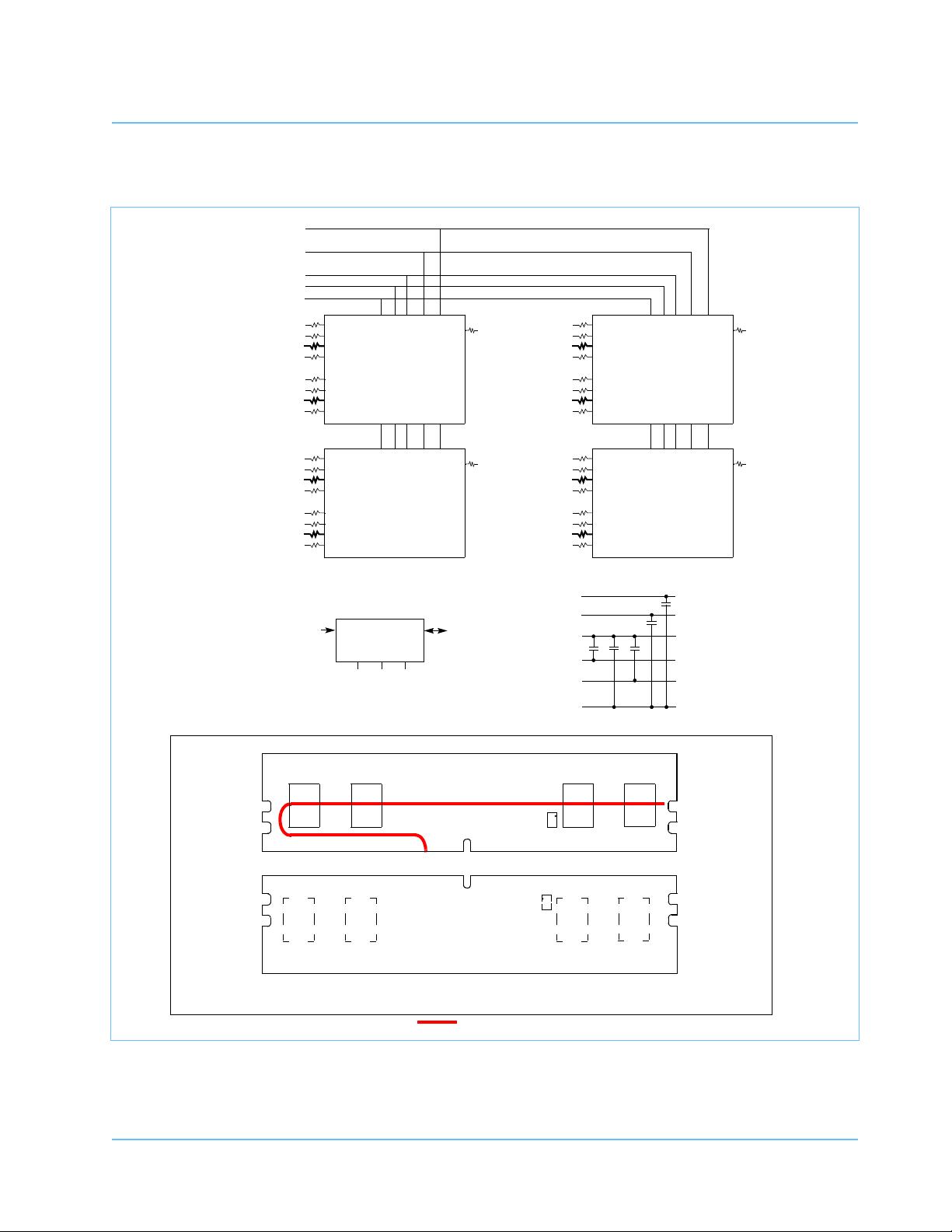

设计文件"Annex C - Raw Card C DDR4 Unbuffered DIMM Design File"包括了"PC4-UDIMM_V100_RC_C0_20150821.brd"和"BOM"文档"PC4-UDIMM_V100_RC_C0_20151116-BOM.docx",它们分别代表了电路板布局和物料清单,用于指导实际的硬件设计和制造。

在模块配置方面,DDR4 Unbuffered DIMM采用单列直插封装(DIMM)形式,内存模块中的SDRAM芯片数量、包层数、行地址和列地址都进行了详细定义。例如,1GB的组织结构为128Mx64,意味着每个SDRAM芯片具有128兆位宽的数据路径和64个存储体;而8GB的组织结构为1Gx64,每个SDRAM芯片有1吉比特的容量,64个存储体。所有这些内存芯片都按照1个Rank(内存列)排列,地址线数量为14/101,其中A16是最高的地址位,与RAS_n信号复用。

SDRAM配置中,支持的DRAM外形尺寸为10.5mm x 14.0mm的96球栅格阵列(FBGA)封装,每个封装内有2个Bank(银行)和1个Bank Group(银行组)。这种配置允许内存模块以更高的速度和更低的功耗运行。

DDR4 Unbuffered DIMM Raw Card C设计规范是构建高效能且兼容的台式机内存模块的基础,它详细规定了内存模块的物理尺寸、电气特性、内存芯片组织和地址映射等关键参数,确保了内存系统的稳定性和性能。

2018-11-20 上传

点击了解资源详情

2021-09-02 上传

2021-09-02 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

中国永

- 粉丝: 5

- 资源: 11

最新资源

- Java毕业设计项目:校园二手交易网站开发指南

- Blaseball Plus插件开发与构建教程

- Deno Express:模仿Node.js Express的Deno Web服务器解决方案

- coc-snippets: 强化coc.nvim代码片段体验

- Java面向对象编程语言特性解析与学生信息管理系统开发

- 掌握Java实现硬盘链接技术:LinkDisks深度解析

- 基于Springboot和Vue的Java网盘系统开发

- jMonkeyEngine3 SDK:Netbeans集成的3D应用开发利器

- Python家庭作业指南与实践技巧

- Java企业级Web项目实践指南

- Eureka注册中心与Go客户端使用指南

- TsinghuaNet客户端:跨平台校园网联网解决方案

- 掌握lazycsv:C++中高效解析CSV文件的单头库

- FSDAF遥感影像时空融合python实现教程

- Envato Markets分析工具扩展:监控销售与评论

- Kotlin实现NumPy绑定:提升数组数据处理性能