Verilog HDL入门:构建算术逻辑处理器教程

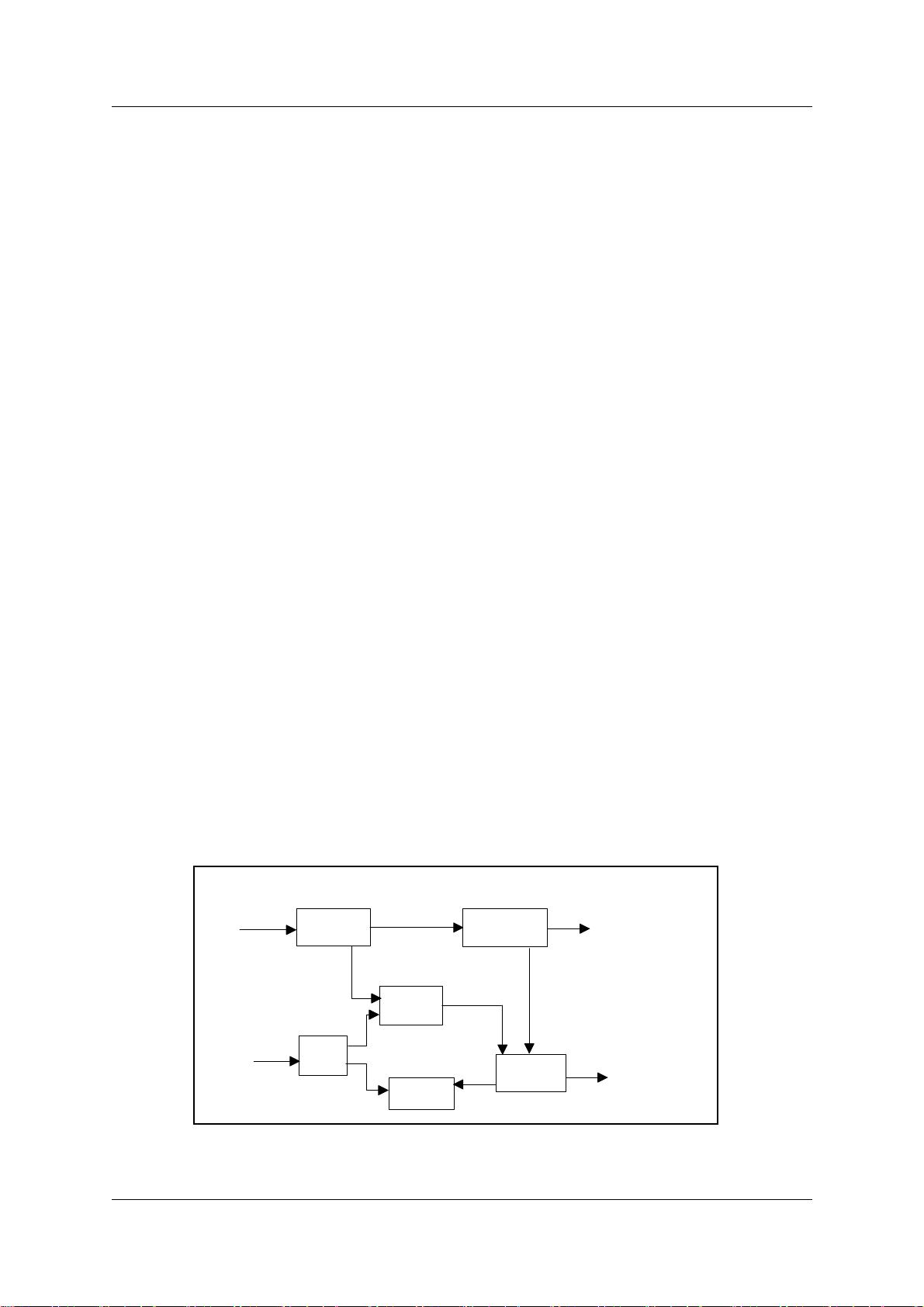

Verilog HDL入门教程是一份针对Verilog语言的详细教程,Verilog是硬件描述语言(Hardware Description Language)的一种,主要用于在高级抽象级别上设计和描述数字系统,如逻辑电路、FPGA和ASIC。该教程从基础知识开始,首先介绍了Verilog语言的基本概念,包括: 1. **定义**:章节1.1详细讲述了Verilog的定义,强调其作为一种结构化设计工具的重要性,用于描述电子系统的功能和行为。 2. **语法**:4.1节介绍了Verilog的基本语法,包括关键字、标识符的书写规范以及算术、关系和逻辑运算符的使用。这些运算符涵盖了算术运算符(如+、-、*、/),关系运算符(>, <, ==等),以及位逻辑运算符(与、或、非)等。 3. **数据类型**:4.5部分着重于数据类型的介绍,包括线网类型和寄存器类型,这些都是构建系统逻辑的基础。 4. **结构建模**:章节3.3讨论了三种建模方式——结构化、行为和数据流描述,这些方式有助于组织和模块化设计。 5. **行为建模**:7章和8章深入到行为建模,涉及case和if-else语句、过程赋值语句、顺序语句块,以及具体的实例演示,这些都是实现系统逻辑控制的重要部分。 6. **模块**:3.1章节介绍了模块的概念,它是设计中的基本单元,包括模块语法、结构和简单的示例,模块化设计是Verilog设计的关键。 7. **格式和注释**:4.2和4.3部分讲述了代码的格式规范和如何添加注释,这对于编写清晰、可读的设计至关重要。 8. **运算符优先级和混合设计描述**:3.3.4部分讨论了不同运算符的优先级以及如何混合使用结构化、行为和数据流描述来描述复杂系统。 通过这份教程,学习者可以掌握如何用Verilog语言设计和实现简单的算术逻辑运算处理器,并了解如何有效地组织和模块化设计,以便于创建大型的数字电路系统。这份教程适合初学者和进阶工程师作为学习和参考材料。

剩余40页未读,继续阅读

- 粉丝: 0

- 资源: 1

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- 计算机人脸表情动画技术发展综述

- 关系数据库的关键字搜索技术综述:模型、架构与未来趋势

- 迭代自适应逆滤波在语音情感识别中的应用

- 概念知识树在旅游领域智能分析中的应用

- 构建is-a层次与OWL本体集成:理论与算法

- 基于语义元的相似度计算方法研究:改进与有效性验证

- 网格梯度多密度聚类算法:去噪与高效聚类

- 网格服务工作流动态调度算法PGSWA研究

- 突发事件连锁反应网络模型与应急预警分析

- BA网络上的病毒营销与网站推广仿真研究

- 离散HSMM故障预测模型:有效提升系统状态预测

- 煤矿安全评价:信息融合与可拓理论的应用

- 多维度Petri网工作流模型MD_WFN:统一建模与应用研究

- 面向过程追踪的知识安全描述方法

- 基于收益的软件过程资源调度优化策略

- 多核环境下基于数据流Java的Web服务器优化实现提升性能

信息提交成功

信息提交成功