FPGA实现高斯滤波技术详解

版权申诉

"该资源详细介绍了如何在FPGA上实现高斯滤波,适用于消除图像中的高斯噪声,常用于图像处理的降噪。通过使用移位寄存器和流水线计算方法,实现高斯滤波器的硬件设计。代码示例展示了具体的模块实例化和接口定义。"

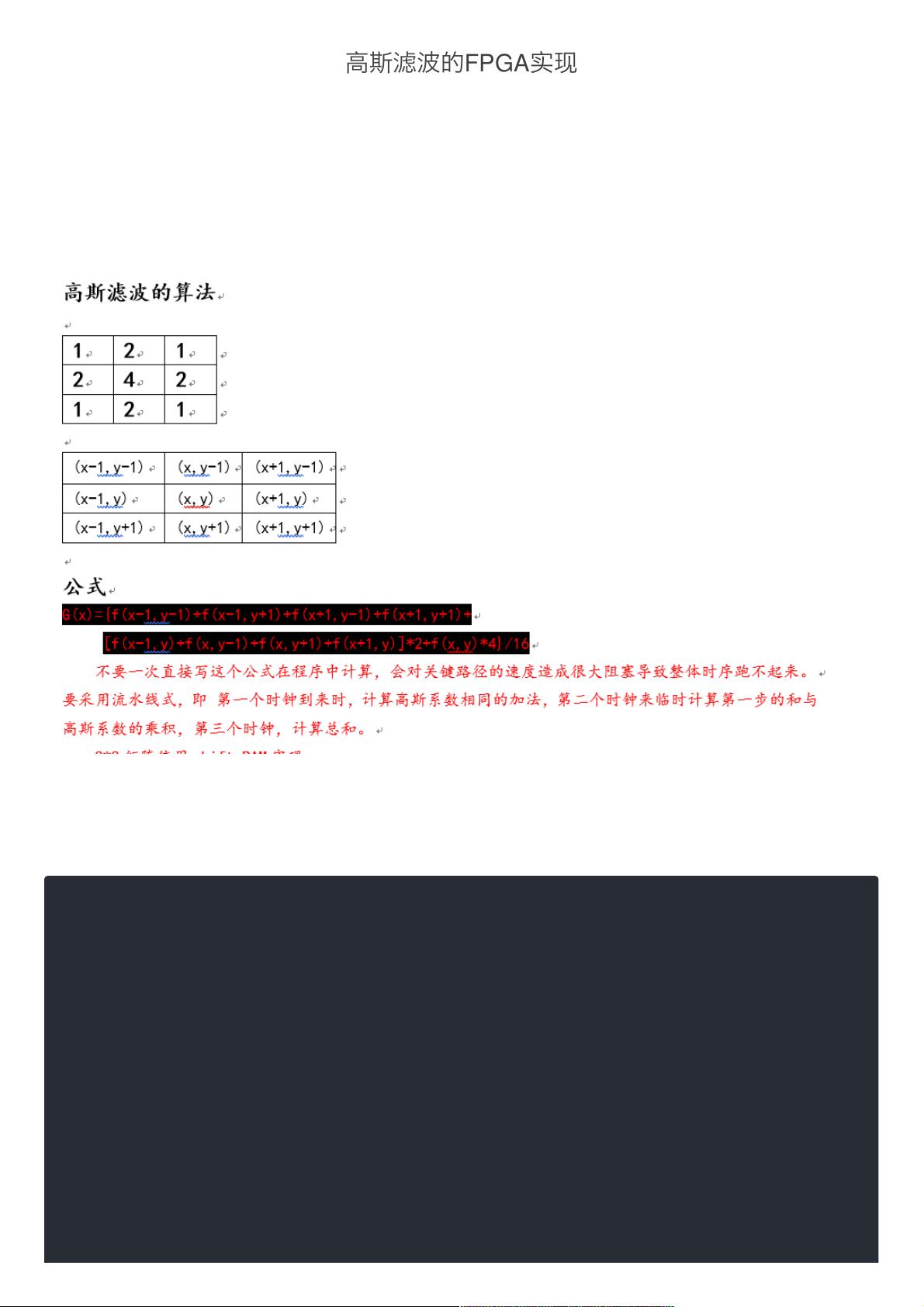

在数字图像处理领域,高斯滤波是一种常用的技术,主要用于降低图像的噪声,特别是由高斯噪声引起的干扰。高斯滤波器的设计基于高斯函数,它能够对图像进行平滑处理,同时保持边缘的清晰度。高斯滤波的过程本质上是对图像中的每个像素进行加权平均,权重是由高斯函数决定的,邻近像素的权重会随着距离的增加而逐渐减小。

在FPGA(Field-Programmable Gate Array)平台上实现高斯滤波,通常利用硬件描述语言(如Verilog或VHDL)进行设计。如资源中所示,可以采用移位寄存器来存储图像的前几行数据,然后按照高斯滤波的计算公式进行流水线处理。这里的`matrix`模块`M_3_3`可能是一个3x3的移位寄存器阵列,用于存储并提供当前及相邻像素值。

代码片段展示了`gs_filter`模块的定义,包括输入和输出信号,如时钟`clk`、复位信号`rst_n`、数据输入`din`以及数据有效性标志`din_vld`等。`DATA_WIDTH`参数定义了数据宽度,通常是8位,表示每个像素的灰度值。此外,还有开始和结束标志`din_sop`和`din_eop`,这些在处理连续数据流时非常有用。

高斯滤波的FPGA实现具有实时性和效率的优势,因为它可以直接在硬件级别执行滤波操作,相比软件实现,速度更快且功耗更低。在实际应用中,这种硬件加速的高斯滤波器可以用于需要快速处理大量图像数据的系统,如视频处理、医学成像或工业检测等领域。

高斯滤波的FPGA实现是一个结合了信号处理理论与数字逻辑设计的复杂任务,需要对图像处理算法、FPGA硬件架构以及相应的编程语言有深入的理解。通过优化设计,可以在FPGA上构建高效、灵活的高斯滤波硬件模块,以满足实时图像处理的需求。

2022-06-12 上传

2016-01-04 上传

2024-08-23 上传

2023-05-28 上传

2023-08-25 上传

2023-05-13 上传

2023-05-15 上传

2023-03-28 上传

_webkit

- 粉丝: 30

- 资源: 1万+

最新资源

- 解决本地连接丢失无法上网的问题

- BIOS报警声音解析:故障原因与解决方法

- 广义均值移动跟踪算法在视频目标跟踪中的应用研究

- C++Builder快捷键大全:高效编程的秘密武器

- 网页制作入门:常用代码详解

- TX2440A开发板网络远程监控系统移植教程:易搭建与通用解决方案

- WebLogic10虚拟内存配置详解与优化技巧

- C#网络编程深度解析:Socket基础与应用

- 掌握Struts1:Java MVC轻量级框架详解

- 20个必备CSS代码段提升Web开发效率

- CSS样式大全:字体、文本、列表样式详解

- Proteus元件库大全:从基础到高级组件

- 74HC08芯片:高速CMOS四输入与门详细资料

- C#获取当前路径的多种方法详解

- 修复MySQL乱码问题:设置字符集为GB2312

- C语言的诞生与演进:从汇编到系统编程的革命