CPU操作与指令执行过程详解

版权申诉

140 浏览量

更新于2024-08-12

收藏 504KB PDF 举报

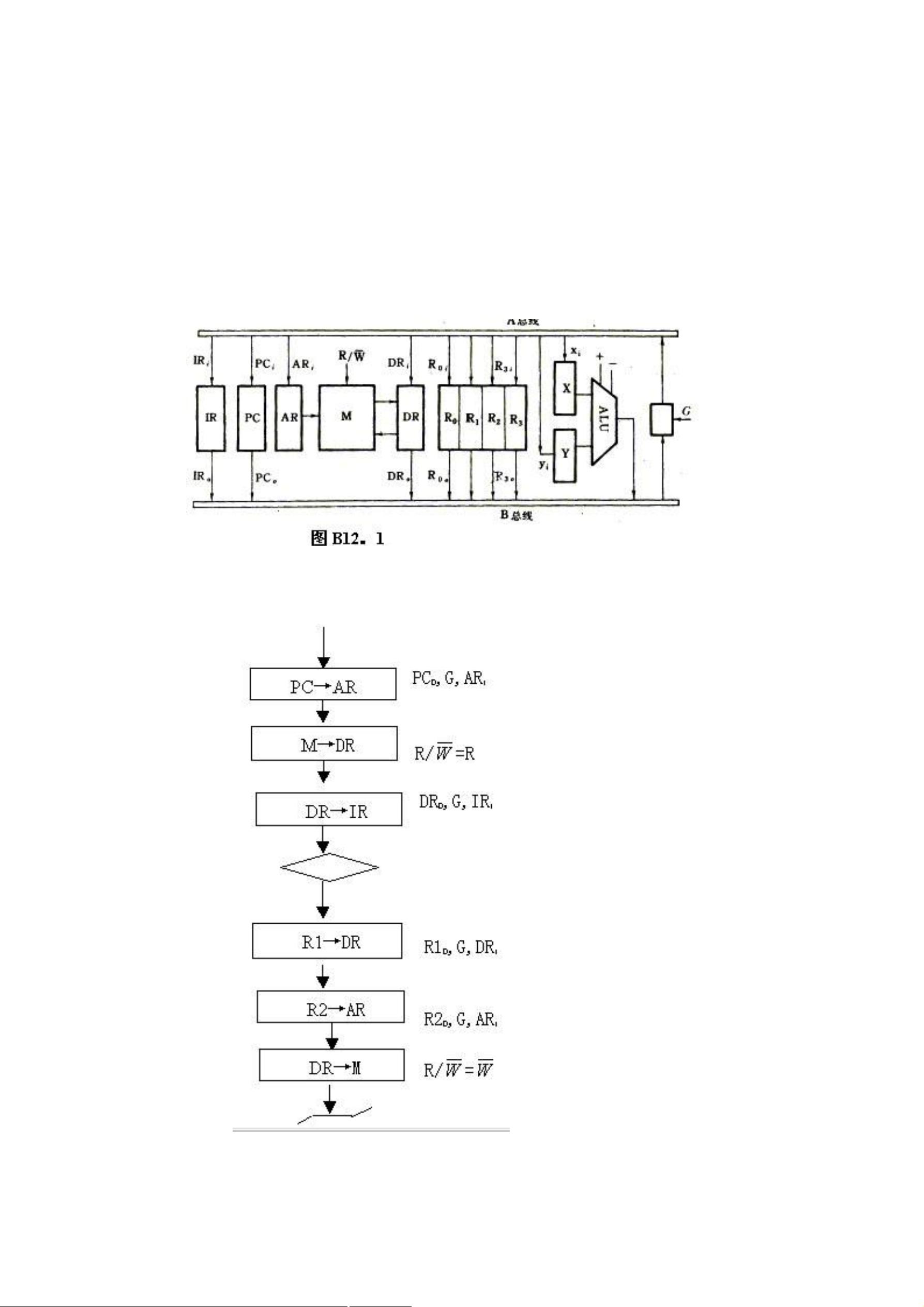

"该资源为第五章中央处理器的习题参考答案,主要涉及CPU内部结构、数据通路、指令执行过程、时序产生器设计、控制存储器容量估算以及微指令编码设计等内容。"

在CPU中,有几种关键的寄存器对指令执行起着重要作用:

1. 指令寄存器(IR):它保存当前正在执行的指令,确保CPU知道要执行的操作。

2. 程序计数器(PC):保存当前指令的地址,每次执行完一条指令后,PC会自动加1,指向下一条待执行的指令地址。

3. 通用寄存器和数据缓冲寄存器(DR):通用寄存器用于存储数据,参与各种算术逻辑运算;数据缓冲寄存器则用于暂时存放运算结果,便于数据的读写操作。

关于数据通路的操作,如图5.15所示,"STAR1,(R2)"指令将寄存器R1的内容存入以R2为地址的内存单元,而"LDA (R3),RO"指令则是将内存中(R3)地址处的内容加载到寄存器R0。这两个指令的指令周期流程图涉及到微操作控制信号序列,这些信号序列协调CPU内部各个部件的工作,以完成指令的读取、执行和数据传输。

时序产生器的设计是CPU工作节奏的关键。在本例中,CPU周期包含三个子阶段T1、T2和T3,对应的逻辑图可以使用移位寄存器实现,确保每个节拍脉冲的准确产生。逻辑表达式T1、T2和T3分别与时钟脉冲的关系体现为:

T1 = C1 ·

T2 =

T3 =

对于控制存储器的容量计算,如果机器有80条指令,平均每个指令由4条微指令组成,其中一条取指微指令是所有指令共用的。那么微指令总数为241条,控制存储器容量为241条微指令乘以每条微指令32位,即1KB。

ALU器件的模式控制码可以通过逻辑表达式来表示不同的算术和逻辑操作。例如,M、S3、S2、S1和C的逻辑表达式分别为:

M = G

S3 = H + D + F

S2 = 1

C = H + D + (E + F)y

最后,对于8条微指令I1到I8,每个微指令包含8位控制字段,要合理安排这些微命令信号,如(e, f, h)和(b, i, j)等,以满足不同微操作的需求。这种安排涉及到微指令设计的优化,以确保高效且灵活的指令执行。

这份习题答案详细讲解了CPU的内部结构、指令执行过程、时序控制、微指令编码等多个重要概念,这些都是理解和设计计算机系统的基础知识。

2022-07-14 上传

2013-10-19 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

2023-07-18 上传

2023-06-19 上传

2024-01-01 上传

2023-07-06 上传

xingwang218

- 粉丝: 1

- 资源: 9万+

最新资源

- 解决Eclipse配置与导入Java工程常见问题

- 真空发生器:工作原理与抽吸性能分析

- 爱立信RBS6201开站流程详解

- 电脑开机声音解析:故障诊断指南

- JAVA实现贪吃蛇游戏

- 模糊神经网络实现与自学习能力探索

- PID型模糊神经网络控制器设计与学习算法

- 模糊神经网络在自适应PID控制器中的应用

- C++实现的学生成绩管理系统设计

- 802.1D STP 实现与优化:二层交换机中的生成树协议

- 解决Windows无法完成SD卡格式化的九种方法

- 软件测试方法:Beta与Alpha测试详解

- 软件测试周期详解:从需求分析到维护测试

- CMMI模型详解:软件企业能力提升的关键

- 移动Web开发框架选择:jQueryMobile、jQTouch、SenchaTouch对比

- Java程序设计试题与复习指南