FPGA上优化的SCL极化码译码设计与性能提升

29 浏览量

更新于2024-08-31

1

收藏 774KB PDF 举报

"基于FPGA的SCL译码算法优化与设计"

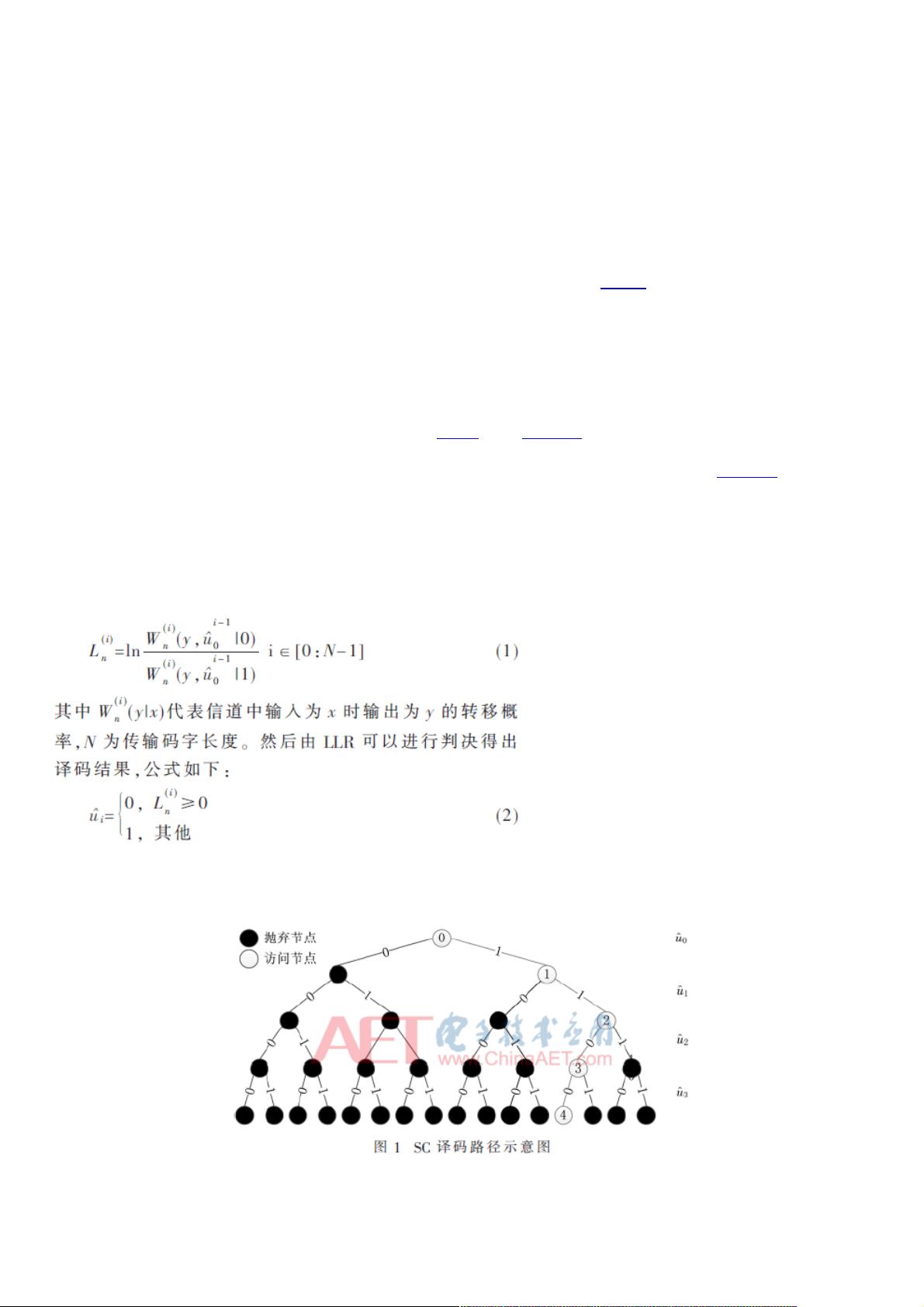

本文主要探讨了如何在FPGA(Field-Programmable Gate Array)平台上优化和设计极化码的SCL(Successive Cancellation List)译码算法,以提高通信系统的效率。极化码,自2008年由Arikan提出以来,因其在二进制离散无记忆信道中的理论性能优势,逐渐在通信领域受到关注。它的核心思想是通过信道结合与拆分来实现信道极化,从而利用“好”信道进行高效数据传输。

传统的SC译码算法虽然简单,但由于其串行处理方式导致译码效率较低。为解决这一问题,SCL译码算法应运而生,它引入列表机制,实现了在复杂度和性能之间的平衡,提高了译码性能。然而,即便如此,SCL算法在软件实现时仍受限于CPU的串行处理模式,限制了整体速度。

在FPGA上实现SCL译码可以充分利用其并行处理能力,显著提升译码速度。文章详细介绍了SCL译码算法,并对其进行了优化,旨在降低资源消耗的同时提高效率。此外,作者还针对FPGA环境对算法进行了定点量化改进,这是为了适应硬件实现的特殊需求,通常包括将浮点运算转换为定点运算,以减小硬件资源占用。

实验结果显示,优化后的SCL译码器在码长为512时,能够达到143.988 MHz的最高译码频率,对应吞吐率为28.79 Mb/s。这一成果表明,该译码器在实际工程应用中具有较高的价值,能够有效提升通信系统的数据处理速度和效率。

总结起来,本文的研究主要贡献在于以下几个方面:

1. 对极化码的SCL译码算法进行了深入研究,优化了其效率,降低了资源消耗。

2. 针对FPGA平台的特点,对SCL译码算法进行了定点量化改进,以便更好地适应硬件实现。

3. 通过硬件仿真和实际FPGA(如Xilinx VC707开发板)上的实现,验证了优化算法的性能,证明了其在通信系统中的实用性。

这一工作不仅对极化码的硬件实现提供了有价值的参考,也为未来类似高速、低延迟的通信系统设计提供了新的思路和技术支持。

2021-07-13 上传

2021-07-13 上传

点击了解资源详情

2022-07-08 上传

2021-07-13 上传

2023-11-17 上传

2023-10-29 上传

2021-07-13 上传

2022-04-12 上传

weixin_38677806

- 粉丝: 5

- 资源: 938

最新资源

- Elasticsearch核心改进:实现Translog与索引线程分离

- 分享个人Vim与Git配置文件管理经验

- 文本动画新体验:textillate插件功能介绍

- Python图像处理库Pillow 2.5.2版本发布

- DeepClassifier:简化文本分类任务的深度学习库

- Java领域恩舒技术深度解析

- 渲染jquery-mentions的markdown-it-jquery-mention插件

- CompbuildREDUX:探索Minecraft的现实主义纹理包

- Nest框架的入门教程与部署指南

- Slack黑暗主题脚本教程:简易安装指南

- JavaScript开发进阶:探索develop-it-master项目

- SafeStbImageSharp:提升安全性与代码重构的图像处理库

- Python图像处理库Pillow 2.5.0版本发布

- mytest仓库功能测试与HTML实践

- MATLAB与Python对比分析——cw-09-jareod源代码探究

- KeyGenerator工具:自动化部署节点密钥生成