4层与6层PCB设计:DDR2/3高速信号完整性与电源策略详解

需积分: 31 131 浏览量

更新于2024-09-12

收藏 1.53MB PDF 举报

本文主要探讨了针对DDR2-800和DDR3高速内存接口在PCB(Printed Circuit Board,印制电路板)设计中面临的信号完整性和电源完整性挑战。随着DDR2达到800Mbps甚至更高,DDR3更是提升至1600Mbps的速率,对PCB的性能要求极高,包括精确的时序匹配、阻抗控制、互联拓扑优化以及电源管理等。

首先,对于受限于层数的PCB,例如4层板,设计者需精巧利用顶层和底层走线,确保GND和VDD平面层的合理布局。Vtt和Vref通常放在VDD层。在6层板中,增加的灵活性使得专用拓扑设计变得更容易,同时减少了电源层与地层之间的距离,从而提高信号完整性(PI)。

在信号线的阻抗控制方面,DDR2要求单端信号线的阻抗为50欧姆,而差分信号(如CLOCK和DQS)需100欧姆终端匹配电阻。所有匹配电阻需连接到VTT,并保持标准值。而DDR3中,ADDR/CMD/CNTRL信号的终端匹配电阻可以选择在40到60欧姆之间,具体取决于SI仿真结果和走线阻抗。差分信号的阻抗始终为100欧姆。

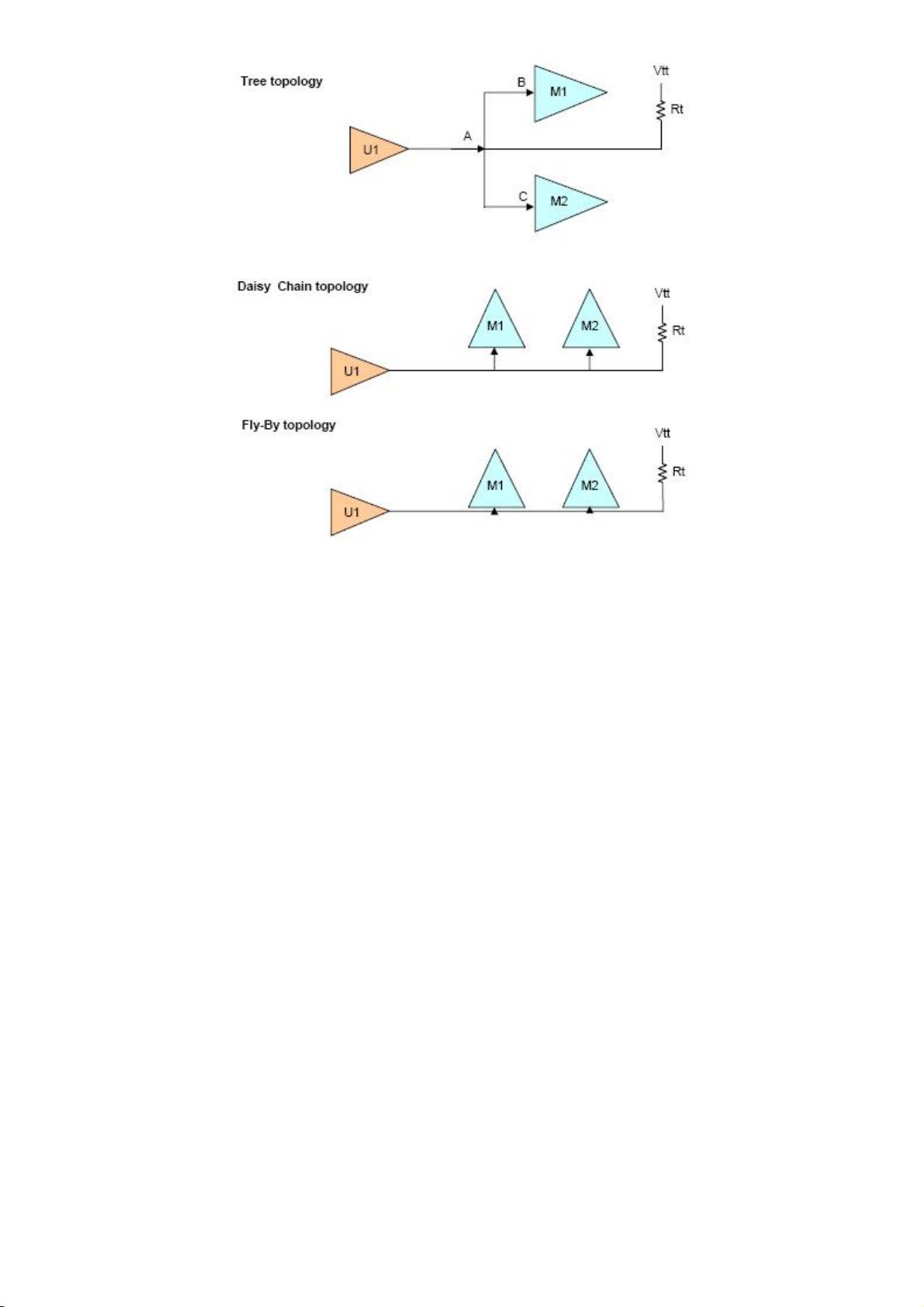

PCB的互联拓扑设计至关重要,它影响着信号之间的串扰和噪声干扰。为了减小这种影响,设计师需要采用有效的布线策略,例如在4层板中,可能需要采用特定的走线路径和隔离技术。

电源完整性是另一个关键考虑因素,特别是在高频率下。电源噪声可能会导致数据错误,因此需要确保电源线的噪声耦合降到最低。设计者可能需要使用多重电源供电方案,以减小瞬态电压变化的影响。

此外,时序匹配和信号完整性分析是通过使用高级EDA(电子设计自动化)工具,如Cadence ALLEGRO SI-230和Ansoft's HFSS,进行计算和仿真来实现的。这些工具能够帮助工程师模拟信号行为,找出潜在问题并进行优化。

总结来说,DDR2-800和DDR3的PCB设计是一门精细的艺术,需要在有限的层面上处理众多复杂的因素,以确保信号质量和系统性能。设计师需不断适应新技术和规范,以应对不断发展的内存标准。

2012-07-19 上传

点击了解资源详情

2011-08-18 上传

点击了解资源详情

2018-08-01 上传

点击了解资源详情

2021-01-19 上传

2022-01-13 上传

2010-12-11 上传

sunghui

- 粉丝: 0

- 资源: 2

最新资源

- MATLAB新功能:Multi-frame ViewRGB制作彩色图阴影

- XKCD Substitutions 3-crx插件:创新的网页文字替换工具

- Python实现8位等离子效果开源项目plasma.py解读

- 维护商店移动应用:基于PhoneGap的移动API应用

- Laravel-Admin的Redis Manager扩展使用教程

- Jekyll代理主题使用指南及文件结构解析

- cPanel中PHP多版本插件的安装与配置指南

- 深入探讨React和Typescript在Alias kopio游戏中的应用

- node.js OSC服务器实现:Gibber消息转换技术解析

- 体验最新升级版的mdbootstrap pro 6.1.0组件库

- 超市盘点过机系统实现与delphi应用

- Boogle: 探索 Python 编程的 Boggle 仿制品

- C++实现的Physics2D简易2D物理模拟

- 傅里叶级数在分数阶微分积分计算中的应用与实现

- Windows Phone与PhoneGap应用隔离存储文件访问方法

- iso8601-interval-recurrence:掌握ISO8601日期范围与重复间隔检查