全数字锁相环中预置可逆分频器设计与实现

61 浏览量

更新于2024-08-30

1

收藏 786KB PDF 举报

"应用于倍频电路的预置可逆分频器设计"

在电子工程领域,倍频电路是一种关键的组成部分,用于将输入信号的频率提升到一个或多个倍数。预置可逆分频器是这类电路的核心组件,它允许灵活地设定分频比例并且能进行正向和反向计数,从而满足全数字锁相环(DLL)的需求。本文重点讨论了预置可逆分频器的设计方法,并通过Simulink和FPGA实现了其模型验证。

预置可逆分频器的工作原理基于比较和控制逻辑。在分频过程中,分频器内部的触发器输出与预设的模值进行比较。当触发器输出与模值匹配时,触发一个符合信号,使计数器回归到初始状态,然后按照预定的计数模式继续工作。这一过程保证了分频器可以在需要时执行正向或反向计数,实现预设的分频比率。

在全数字锁相环中,分频器的作用至关重要。传统的锁相环系统多由模拟组件构成,而现代设计倾向于使用全数字方案,这包括数字鉴相器、数字环路滤波器、压控振荡器以及本文重点讨论的预置可逆分频器。全数字设计的优点在于精度高、灵活性强,同时易于集成和调试。

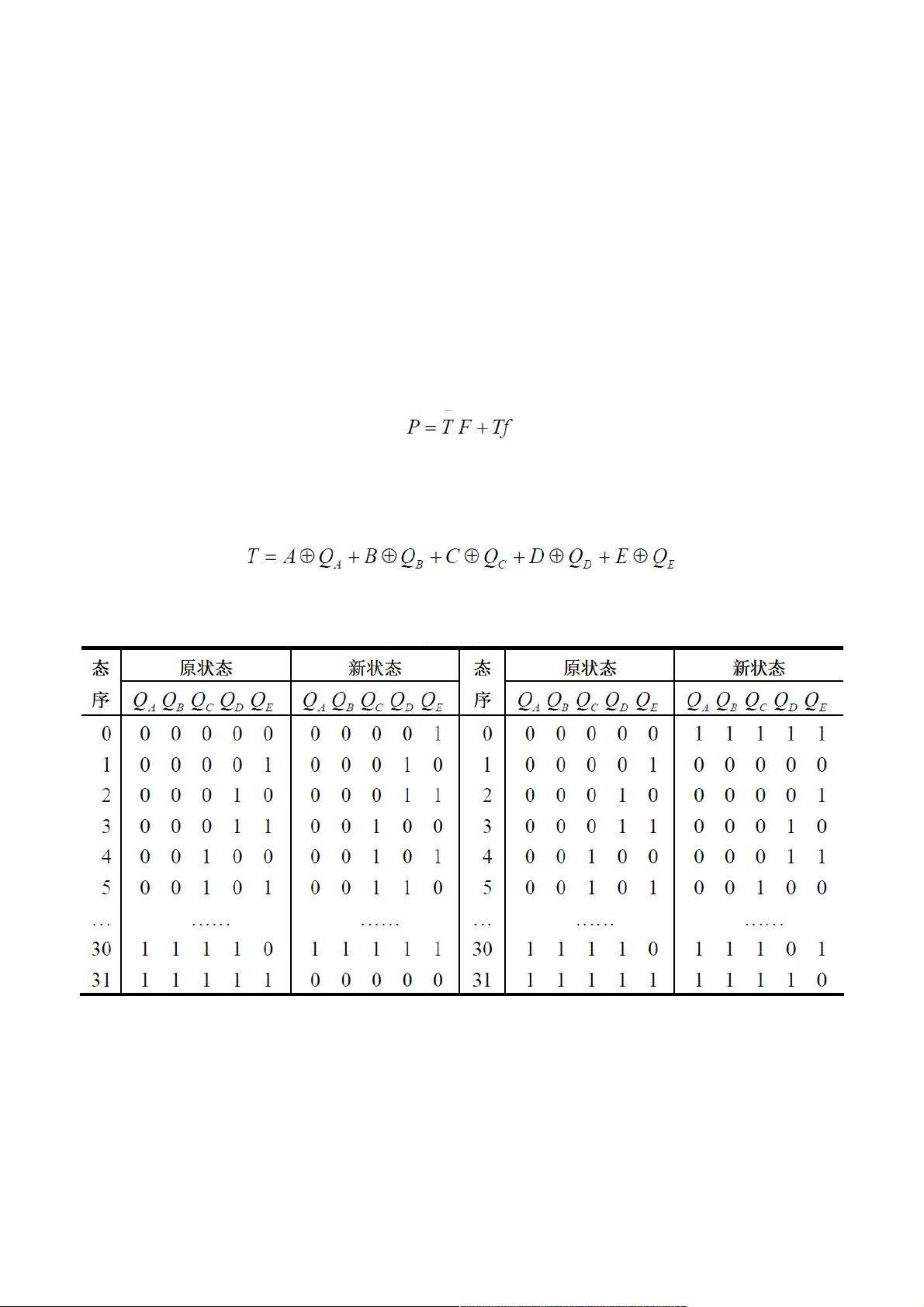

预置可逆分频器的设计涉及触发器的驱动函数推导。这些驱动函数决定了触发器在不同状态下的行为,包括正常计数和强迫跳变到预设状态。通常,每个触发器会受到两种控制信号的影响:一是常规的卡诺图控制函数,决定了计数器的正常工作流程;二是符合函数,用于在特定条件下强制触发器跳变,实现可逆分频。

在具体实现上,文章提到利用Simulink进行系统级仿真,这是一种基于MATLAB的模块化仿真工具,适合设计复杂的数字逻辑系统。而FPGA(Field-Programmable Gate Array)则提供了硬件实现平台,允许开发者快速原型验证和优化设计。通过这两个工具,作者能够建立并测试分频器模型,验证其预置模和可逆分频的功能。

实验结果证实了该设计的有效性,表明预置可逆分频器能满足倍频电路对可预置模和可逆分频的需求。表1和表2展示了分频器的状态转换和计数值与触发器当前值的关系,它们是设计的关键部分,确保了分频器在不同模式下的正确运行。

本文介绍了一种应用于倍频电路的预置可逆分频器设计方法,涵盖了理论分析、驱动函数推导、仿真模型建立和硬件实现。这种分频器为全数字锁相环提供了更高效、灵活的频率处理能力,对现代通信系统和数字信号处理应用具有重要意义。

224 浏览量

143 浏览量

224 浏览量

点击了解资源详情

点击了解资源详情

110 浏览量

点击了解资源详情

490 浏览量

weixin_38748740

- 粉丝: 4

- 资源: 940

最新资源

- 一个帮助实现条形码扫描的库-Android开发

- casile:CaSILE工具包,采用SILE和其他向导的图书出版工作流程

- TextureSwiftSupport:一个使我们获得DSL来在Texture中定义布局规范的库[如SwiftUI]

- 高端大气星级酒店展示网站静态模板.zip

- PING-开源

- 雷达成像中的时频分析成像

- WebRtcAecmSample:这是一个aecm示例(使用webrtc)

- bluetooth.rar_android 蓝牙_android bluetooth_android蓝牙_蓝牙_蓝牙通信

- area_of_a_regular_polygon

- LibraryPractice_20210327

- ruby-on-rails-cassandra:Ruby on Rails与Cassandra

- 泛型MakeGeneric方法应用实例.rar

- 影刀RPA系列公开课3:网页自动化——数据抓取.rar

- formation_control-master.zip_formation control_formation_control

- matlab标注字体代码-MATLAB-Tools:为MATLAB生成的一组脚本,这些脚本可能在您自己的项目和文件中有用

- flex-masonry:用CodeSandbox创建