FPGA实现线性FIR数字滤波器设计与优化

版权申诉

102 浏览量

更新于2024-07-04

收藏 1.96MB DOC 举报

"基于FPGA实现线性FIR数字滤波器"

本文主要探讨了如何使用现场可编程门阵列(FPGA)技术来实现线性FIR(有限冲击响应)数字滤波器,该滤波器在宽带信号处理中有着广泛应用,尤其是在目标检测和分类中的频谱分析。FIR滤波器因其线性相位特性及稳定性成为设计首选。

一. 绪言

1.1 课题背景

在现代通信和信号处理领域,滤波器是不可或缺的组件,特别是在雷达、通信系统以及音频和视频处理中。FPGA由于其可重构性和高性能计算能力,成为了实现数字滤波器的理想平台。

1.2 课题研究的目的和意义

本研究旨在设计并实现一种高效、灵活的FPGA-based FIR滤波器,通过优化算法降低硬件资源需求,同时保证系统运行速度,提高信号处理的实时性与精度。

二. 滤波器设计原理

2.1 滤波器的基本概念

滤波器的主要作用是筛选信号中的特定频率成分,包括低通、高通、带通和带阻滤波器等。滤波原理基于傅立叶变换,通过对信号进行时域与频域的转换来实现对频率成分的选择性保留或消除。

2.1.1 滤波原理

滤波器通过改变信号的频率响应来达到滤波目的,线性滤波器保证了信号相位与频率的关系为线性的。

2.1.2 滤波器的分类

滤波器通常分为IIR(无限冲击响应)和FIR两类。FIR滤波器因其易于实现线性相位和稳定性能而受到青睐。

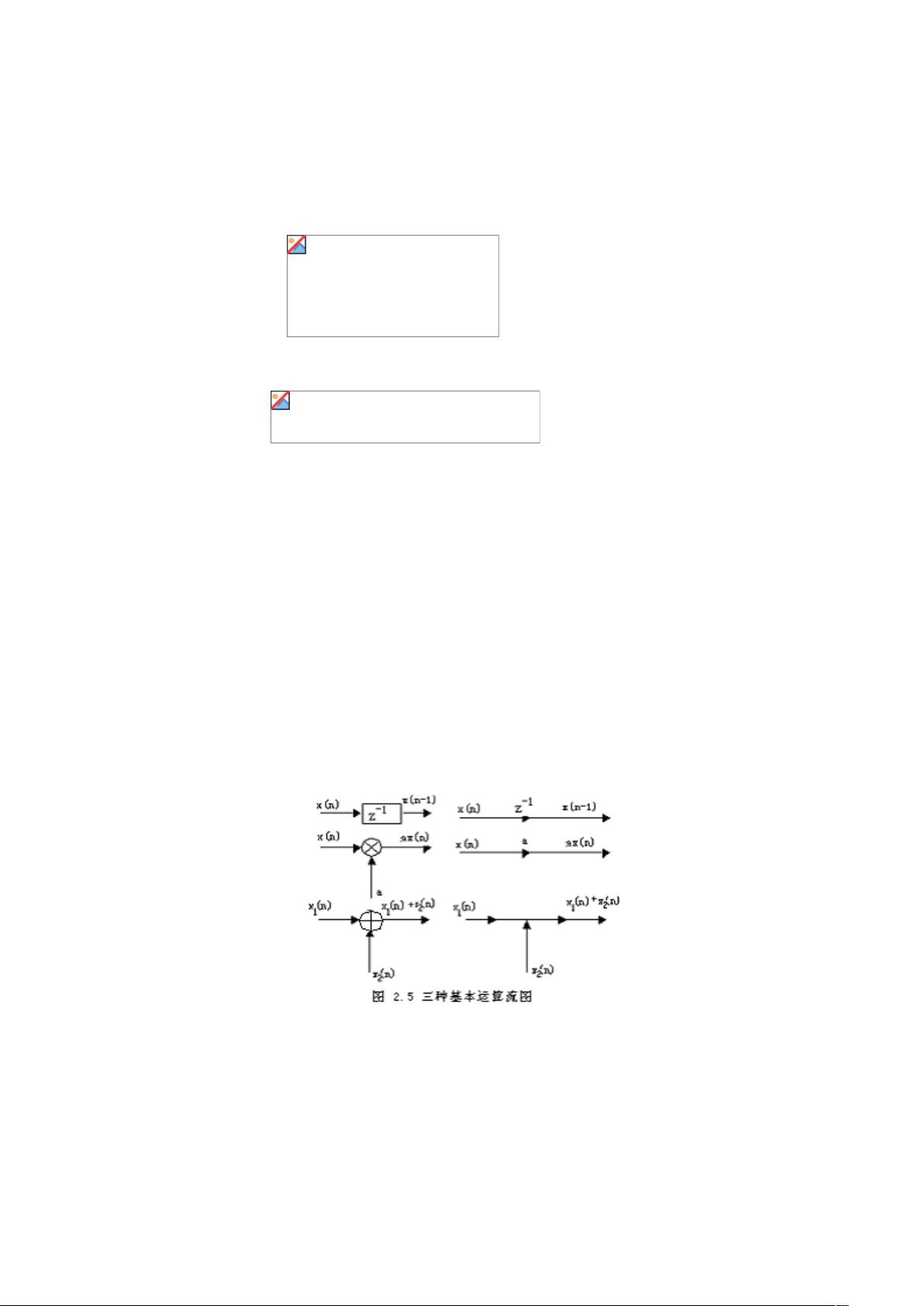

2.1.3 数字滤波器结构的表示方法

数字滤波器可以采用直接型、级联积分梳状滤波器(CIC)、并行和串行结构等多种表示方法。

2.2 有限冲击响应(FIR)滤波器的基本概念

FIR滤波器的输出是输入序列与权重系数的线性组合,其特点包括线性相位、可设计任意频率响应形状、无自振荡等。

三. FIR数字滤波器的设计思路

设计FIR滤波器的关键在于乘加运算,本文提出利用分布式算法和查找表结构来实现乘法器,减少存储需求。通过多级流水线的方式,可以提高运算速度,实现高速滤波。VHDL作为硬件描述语言被用于编写实现这一设计的代码。

总结,本研究结合FPGA的并行处理优势,提出了一种优化的FIR滤波器设计方案,不仅降低了存储需求,还保证了系统的运行效率。这一成果对于提高信号处理系统的性能和灵活性具有重要的实践价值。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-09-18 上传

2023-06-20 上传

2023-06-20 上传

2021-10-05 上传

2021-10-04 上传

2021-10-04 上传

智慧安全方案

- 粉丝: 3814

- 资源: 59万+

最新资源

- 全国江河水系图层shp文件包下载

- 点云二值化测试数据集的详细解读

- JDiskCat:跨平台开源磁盘目录工具

- 加密FS模块:实现动态文件加密的Node.js包

- 宠物小精灵记忆配对游戏:强化你的命名记忆

- React入门教程:创建React应用与脚本使用指南

- Linux和Unix文件标记解决方案:贝岭的matlab代码

- Unity射击游戏UI套件:支持C#与多种屏幕布局

- MapboxGL Draw自定义模式:高效切割多边形方法

- C语言课程设计:计算机程序编辑语言的应用与优势

- 吴恩达课程手写实现Python优化器和网络模型

- PFT_2019项目:ft_printf测试器的新版测试规范

- MySQL数据库备份Shell脚本使用指南

- Ohbug扩展实现屏幕录像功能

- Ember CLI 插件:ember-cli-i18n-lazy-lookup 实现高效国际化

- Wireshark网络调试工具:中文支持的网口发包与分析