使用Quartus II进行ALTERA FPGA时序分析

需积分: 9 88 浏览量

更新于2024-07-20

收藏 12.87MB PPT 举报

“ALTERA FPGA时序分析涉及到设计验证的关键环节,包括时序分析、内部及系统级模拟、形式验证、功耗分析、信号完整性分析以及系统内的测试。Quartus II软件提供了支持这些验证过程的功能,如TimeQuest Timing Analyzer用于时序分析,ModelSim-Altera [Starter] Edition及第三方工具支持模拟,PowerPlay Power Analyzer处理功耗分析,以及调试工具支持系统内测试。”

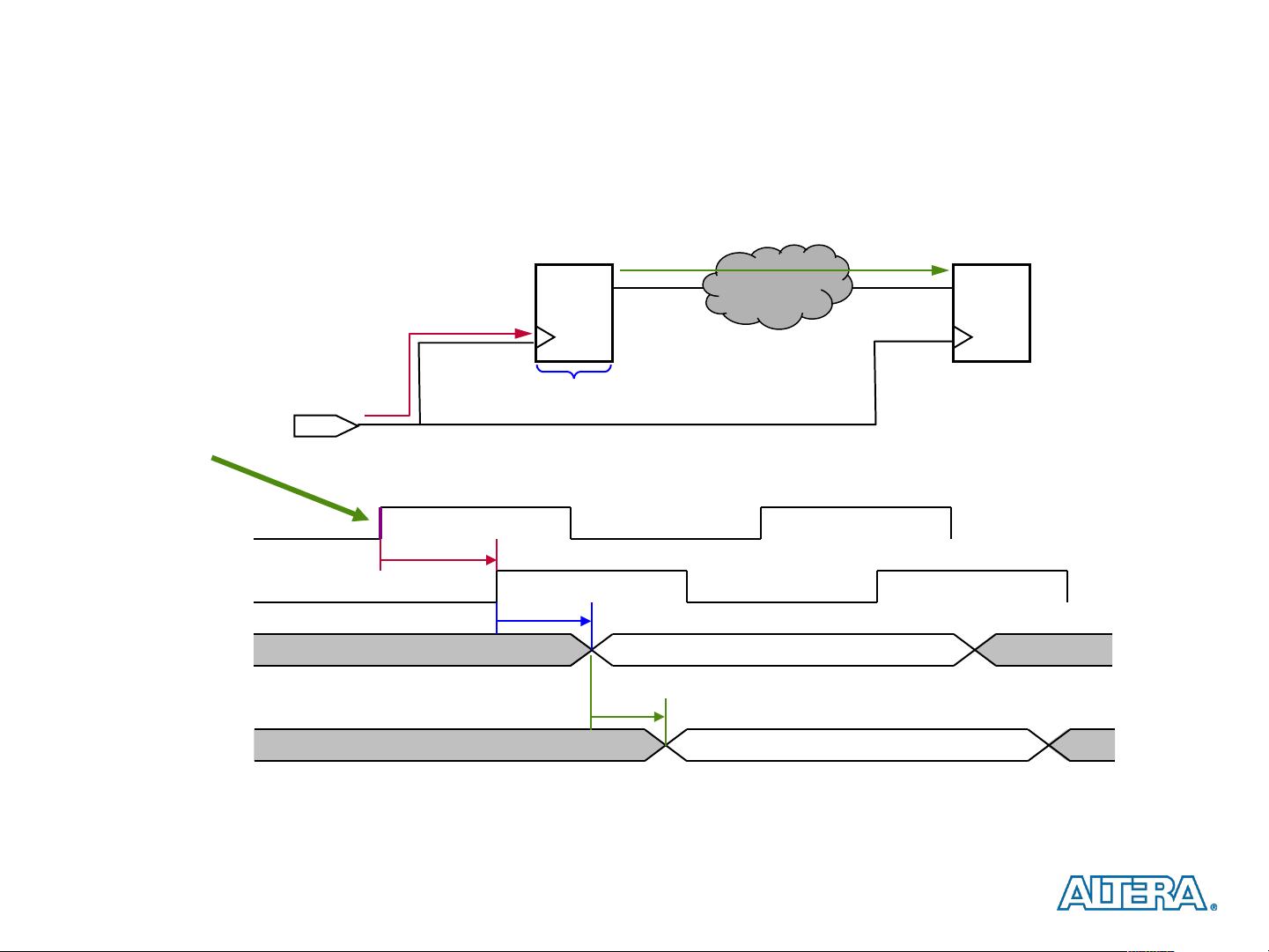

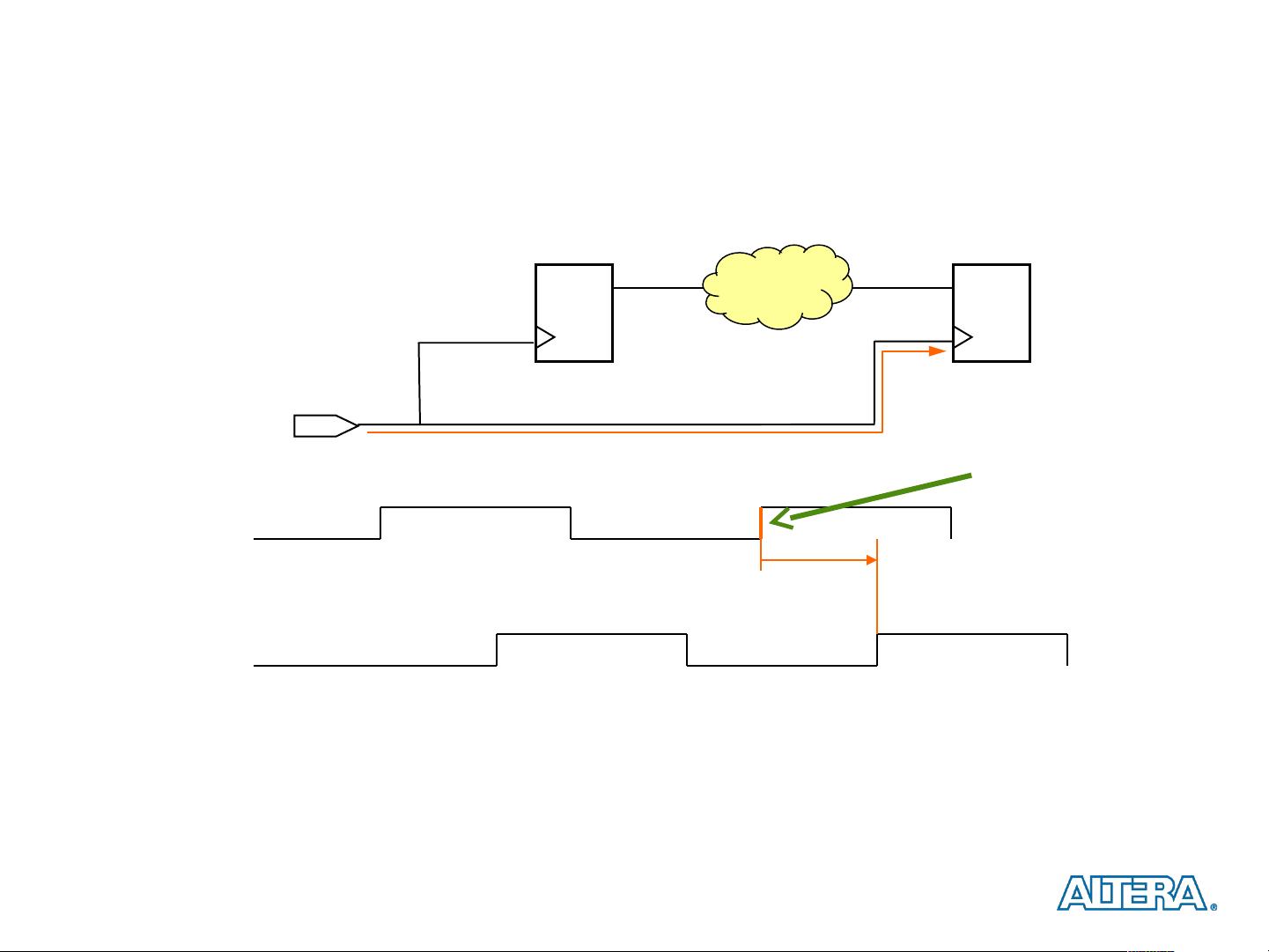

在电子设计自动化(EDA)领域,ALTERA FPGA(现场可编程门阵列)的时序分析是确保电路设计满足速度要求和功能正确性的重要步骤。时序分析旨在确定设计中的信号从输入到输出的传播时间,以确保在整个工作电压和温度范围内所有路径都能满足时序约束。这关系到FPGA在实际应用中的性能和稳定性。

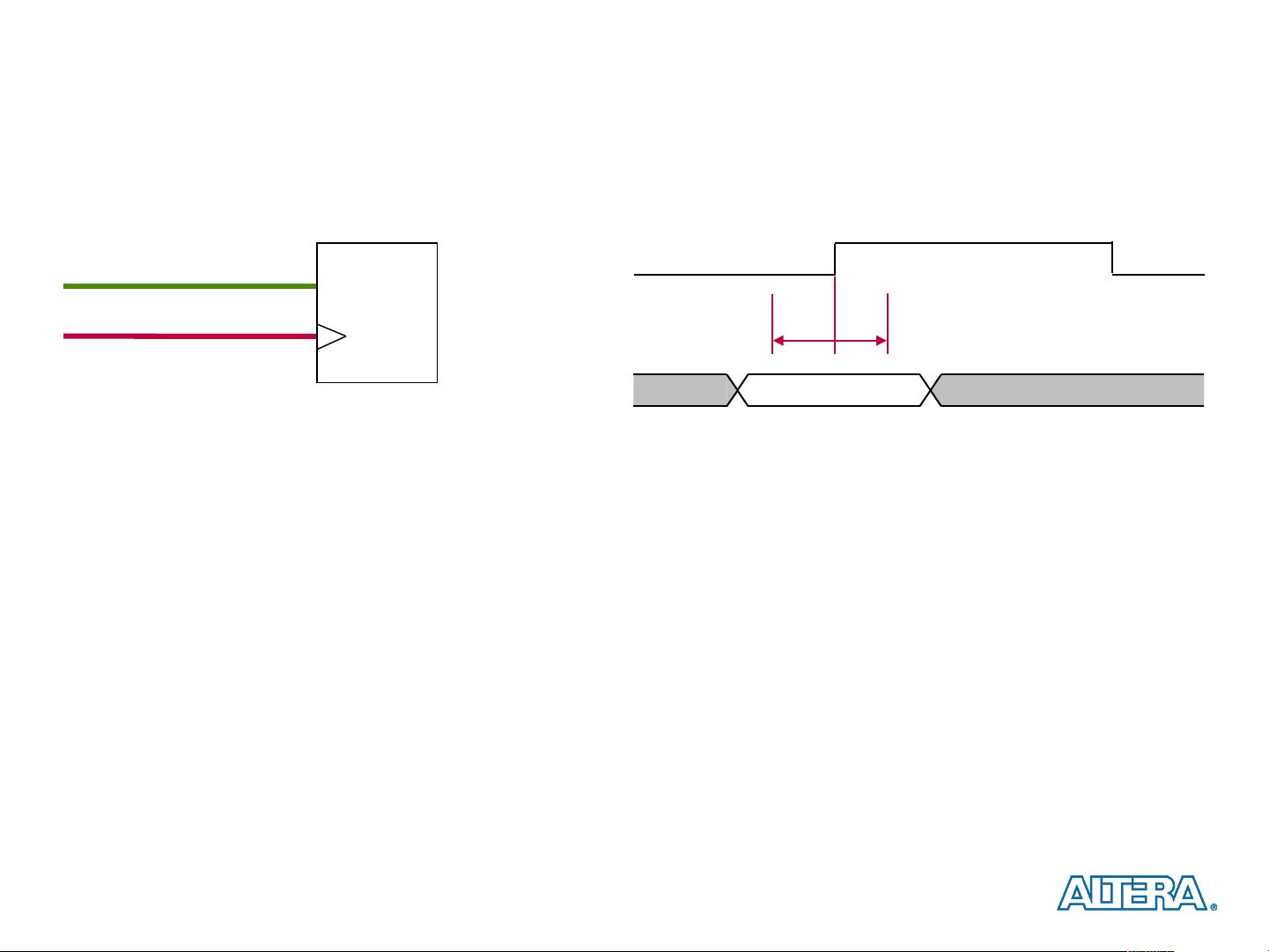

Quartus II是ALTERA公司提供的一款强大的FPGA设计软件,它包含了一系列辅助和加速验证过程的工具。TimeQuest Timing Analyzer是Quartus II的核心组件之一,它能够进行全面的时序分析,帮助设计师识别设计中的关键路径,优化布局布线,确保设计满足时钟速度要求。用户可以通过构建SDC(时序约束脚本)文件来定义设计的时序限制,这些文件可以指定时钟路径、建立时间和保持时间等关键参数。

在设计验证中,除了时序分析外,内部和系统级模拟也是必不可少的。ModelSim-Altera [Starter] Edition是一款模拟器,可以仿真设计的逻辑行为,验证其在不同情况下的表现。形式验证是一种更为严谨的验证方法,它通过数学方法证明设计的正确性,避免了传统的基于测试向量的模拟可能存在的疏漏。

功耗分析是现代电子设计中不可忽视的部分,PowerPlay Power Analyzer能够预测和优化设计的静态和动态功耗,从而实现低功耗设计。信号完整性分析则关注信号在传输过程中的质量和完整性,防止由于噪声、反射等问题导致的信号失真。

最后,系统内的测试允许设计师在真实环境中测试和调试设计,这通常是通过JTAG(联合测试行动组)接口或内置的调试模块实现的。这些工具和方法确保了ALTERA FPGA设计不仅在理论上正确,而且在实际应用中也能表现出预期的性能。

通过学习和掌握上述知识,设计师能够对ALTERA FPGA进行有效的时序分析,创建满足时序约束的高质量设计,并进行全方位的验证,以保证设计的成功实施。

131 浏览量

231 浏览量

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

169 浏览量

370 浏览量

点击了解资源详情

ylkevin

- 粉丝: 0

最新资源

- Ubuntu/Mac工作站的Ansible自动化配置手册

- 掌握核心,JAVA初级面试题解析大全

- 自我测试指南:成功方法与技巧大公开

- ReactSortableHOC实现动画化可排序的触摸友好列表

- SAE开源平台:整合Spring与SMS通讯功能

- 温尼伯公交信息实时查询系统开发

- JAVA实现的可部署仓储管理信息系统详解

- ArquitecturaClass软件:探讨JavaScript的架构设计

- 掌握React项目构建与部署的capstone3指南

- 详细解读车辆购置附加费征收办法

- Java实现学生成绩管理系统的设计与功能

- 易语言实现的MDB网络数据库模块源码解析

- 艺佰设计提供清新企业Discuz模板下载

- 掌握Python中的MLEnsemble实现高效集成学习

- Java实现读取搜狗细胞词库scel文件教程

- 探索城市星球的崛起:Nature & Science精选论文