CPLD实现的高精度脉冲信号源设计与优势

150 浏览量

更新于2024-09-02

1

收藏 1.14MB PDF 举报

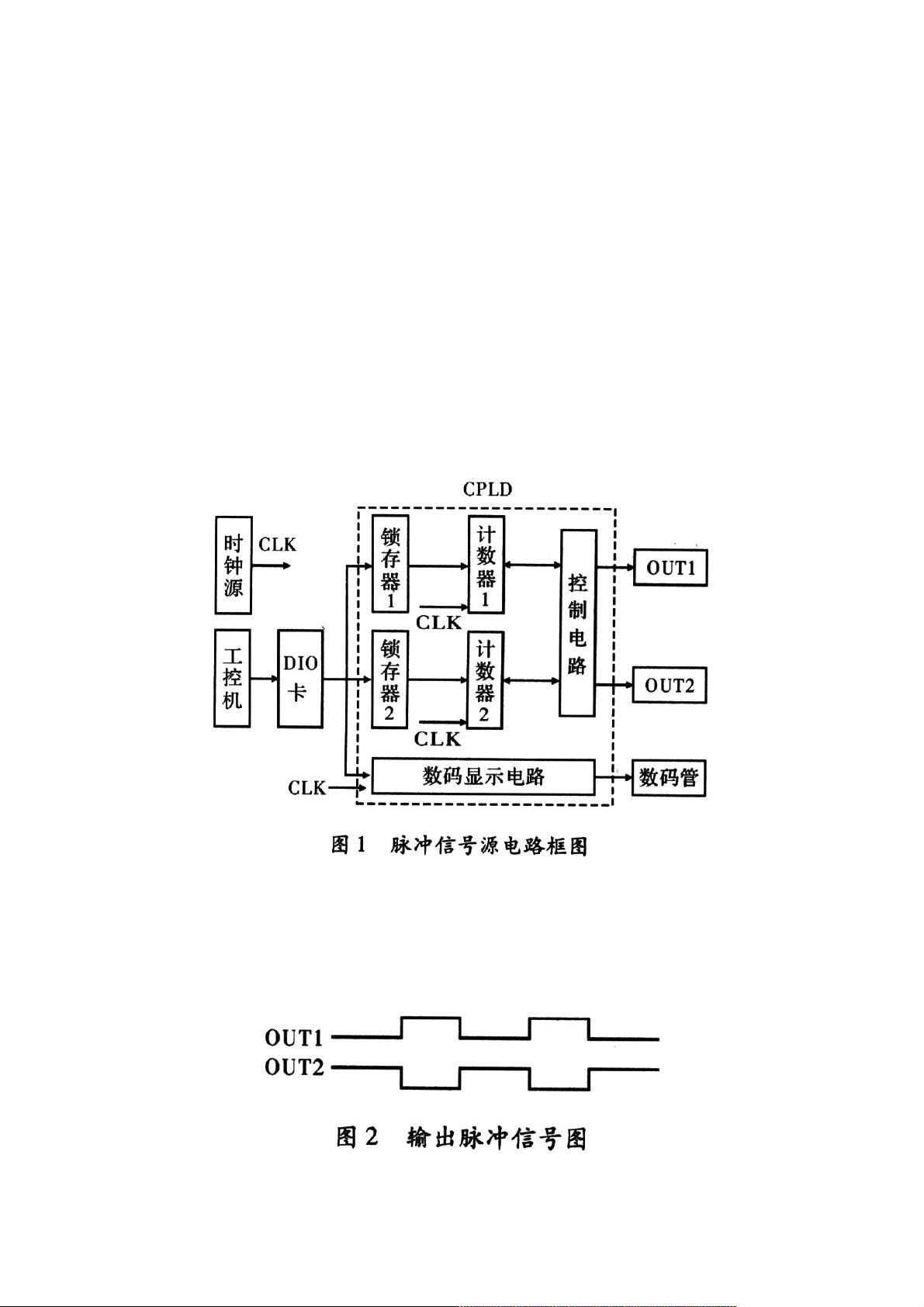

本文主要探讨了脉冲信号源的一种创新实现方法,采用可编程逻辑器件CPLD(Complex Programmable Logic Device)为核心,具体来说,是使用了Ahera公司MAX7000系列中的EPM7128SLC84—10器件。这种CPLD作为脉冲信号源的核心组件,具有高速度、高密度和高性能的特点,使得脉冲信号的输出频率和步进可得到显著提升。

文章首先指出,相比于单片机产生的脉冲信号源,CPLD实现的优势在于不受硬件限制,可以提供更高的频率和更小的步进调整,这得益于CPLD的高级设计和CMOS EPROM技术。MAX7000系列产品的高集成度和多端口特性使得输入延迟极短,支持多种系统时钟和可编程速度/功率控制,使得电路设计更为灵活。

EPM7128SLC84—10这款CPLD具备128个逻辑宏单元,2500个门电路,8个逻辑阵列块,以及68个I/O管脚,具有高速等级和较高的时钟频率,非常适合高频脉冲信号源的制作。整个脉冲信号源电路由以下几个关键部分构成:80MHz有源晶振提供时钟信号,锁存器用于存储频率和占空比的设定值,16位计数器根据锁存器的值进行定时,控制电路接收计数器信号并决定何时切换计数器的工作,确保脉冲信号的准确生成。

通过工控机的I/O板卡,用户可以方便地设置和调整脉冲信号的参数,如频率和占空比,并通过数码管实时显示设置结果,便于实时监控和调试。这种设计提高了信号源的灵活性和精确度,使得脉冲信号的输出更加稳定和可控。

这篇文章详细介绍了如何利用CPLD技术来构建一个高效、精准且易于调节的脉冲信号源,这对于电子测量和信号处理领域有着重要的应用价值。通过CPLD的灵活编程能力,可以满足不同应用场景对脉冲信号特性的需求,提升了信号源的技术含量和市场竞争力。

2021-01-19 上传

2020-11-09 上传

2020-10-21 上传

2020-10-22 上传

点击了解资源详情

点击了解资源详情

2020-08-31 上传

2021-07-26 上传

2013-04-05 上传

weixin_38726712

- 粉丝: 2

- 资源: 958

最新资源

- browser-power:可以在浏览器中运行的客户端javascript展示

- 用于计算方位角、高程、儒略日期、GMST 和 LMST 的天文软件。:该软件将 RA 和 DEC 转换为方位角和高程,以及许多其他内容-matlab开发

- Curso_Udemy_testes_integracao_Spring_Boot:Spring Boot e JUnit和Java集成测试

- 基于PHP的最新版有米埠百信卡盟源码.zip

- React30DayGrind:自我描述

- GK888 internal font.zip

- dicebag:使用骰子符号滚动骰子的 Discord 机器人

- ESP32-HomeKit-Night-Light:使用具有WS2812 LED的ESP32板与Apple HomeKit兼容的小夜灯

- new-portfolio-with-react-bootstrap:示范网站

- webpack5-federation:快速秒杀

- 系列计算器:Calculadora deSéries和MatériadeCálculoII

- quizapp

- 学生公寓管理系统ASP毕业设计(源代码+论文).zip

- evdi-hello:evdi库的测试库

- esiil:ESI API 接口

- Mapping_Earthquakes