CPLD实现的高精度单片机脉冲信号源设计

71 浏览量

更新于2024-08-31

收藏 1.14MB PDF 举报

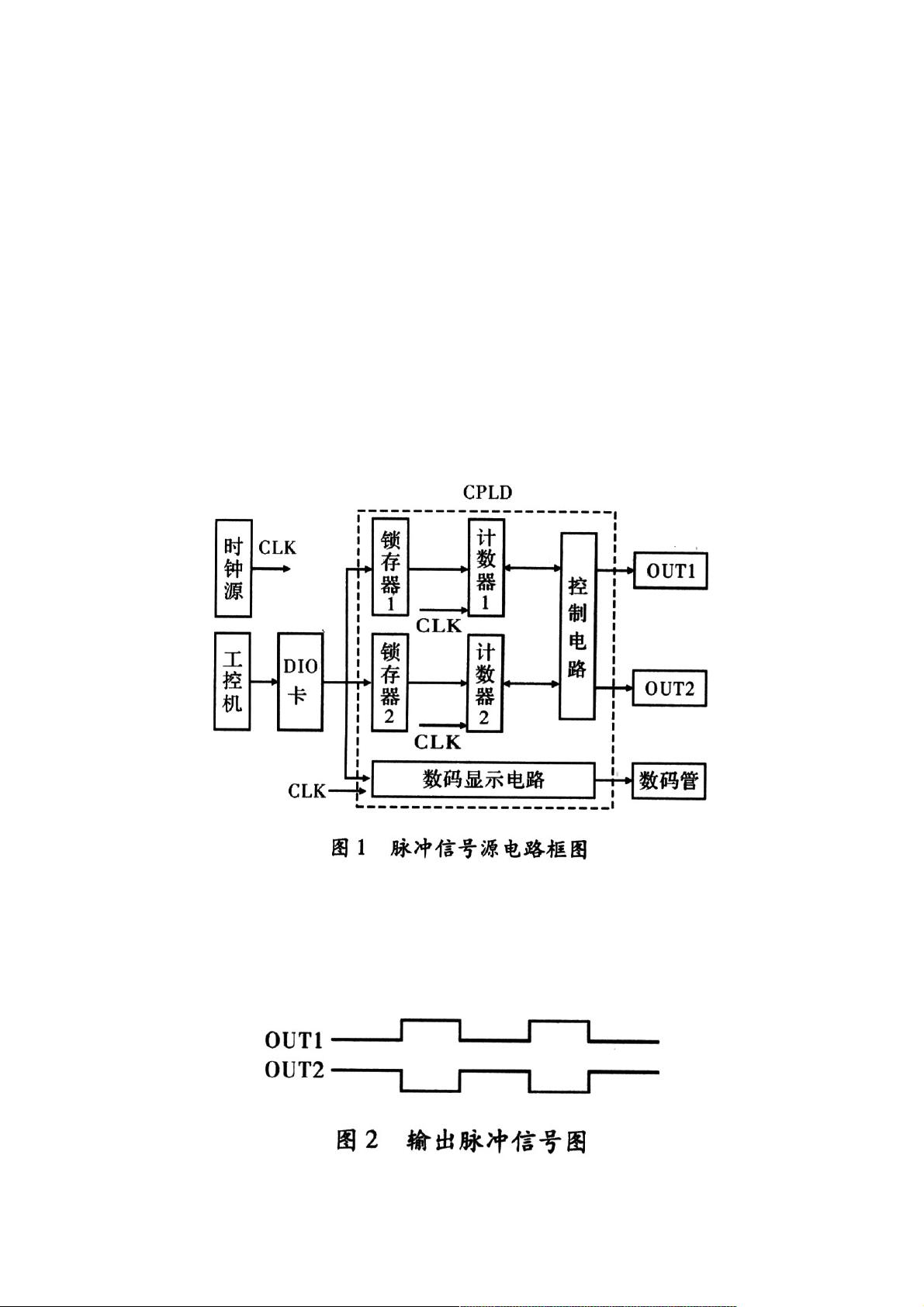

"本文介绍了以CPLD(复杂可编程逻辑器件)为核心,构建高精度、高频率、小步进脉冲信号源的方法。通过工控机的I/O板卡设置脉冲参数,实现参数的灵活调整,并利用高速CPLD提高输出频率和减少步进,确保了信号源的精度和易用性。设计中选用了AHERA公司的EPM7128SLC84-10,该器件属于MAX7000系列,拥有快速的传输延迟和可编程的特性,适合高速脉冲信号的生成。系统主要由时钟源、锁存器、计数器、控制电路、驱动电路和数码管显示电路组成。时钟源使用80MHz有源晶振,锁存器用于存储预设的频率和占空比数据,计数器则根据这些数据进行定时,控制电路则负责协调各个部分的工作,确保脉冲信号的准确输出。"

在单片机脉冲信号源的实现中,通常受限于单片机的时钟频率、指令执行时间和指令数量。然而,使用CPLD作为核心的解决方案可以克服这些限制。CPLD是一种可编程逻辑器件,允许硬件级别的定制,因此可以实现更高的频率输出和更精细的步进控制。文中提到的CPLD型号EPM7128SLC84-10,属于MAX7000S系列,具备高密度和高速度的特性,最高时钟频率可达147.1MHz,适合需要高频脉冲的应用。

系统设计中,80MHz的有源晶振作为主时钟源,提供稳定的时钟信号。数据的设定和显示是通过工控机与I/O板卡的交互完成的,这样可以方便地调整脉冲源的参数,如频率和占空比,并通过数码管实时显示当前设定。为了实现高精度计时,采用了16位计数器,并通过8位锁存器分两次输入数据,以适应16位计数器的需求。计数器1和计数器2交替工作,一旦达到设定的时间,就会向控制电路发送信号,从而控制脉冲的产生。

控制电路是整个系统的协调中心,它接收计数器的信号,适时切换计数器的工作状态,确保脉冲信号的连续性和准确性。同时,驱动电路负责将CPLD生成的信号放大以满足外部设备的需求。这种设计方案使得脉冲信号源不仅具有高频率、高精度,而且易于参数调整,对于需要灵活控制脉冲特性的应用场合,如通信、测试测量和自动化设备,具有显著的优势。

2020-08-31 上传

2021-01-19 上传

2020-11-09 上传

2020-08-31 上传

点击了解资源详情

2013-04-05 上传

2024-03-10 上传

2020-08-13 上传

2021-07-26 上传

weixin_38626080

- 粉丝: 8

- 资源: 973

最新资源

- dwr入门级电子书,容易阅读

- Visual Studio .NET使用技巧手册

- Struts 中文API

- 搭建嵌入式开发环境 基础文档

- 走出 JNDI 迷宫.pdf

- Oracle PL-SQL语言初级教程

- 自从计算机问世以来,程序设计就成了令人羡慕的职业,程序员在受人宠爱之后容 易发展成为毛病特多却常能自我臭美的群体。

- 再次推荐DOM4J资料 pdf

- 107个常用Javascript语句

- CAN入门技术资料 CAN入门书

- LoadRunner8.1 中文版PDF教程

- java基础教程(适合初学者)

- 概率统计与数理统计知识点

- Selective arq 实现

- ArcGIS Engine开发实例教程

- C8051F35x中文版