CPLD实现的高精度脉冲信号源设计

134 浏览量

更新于2024-08-29

1

收藏 448KB PDF 举报

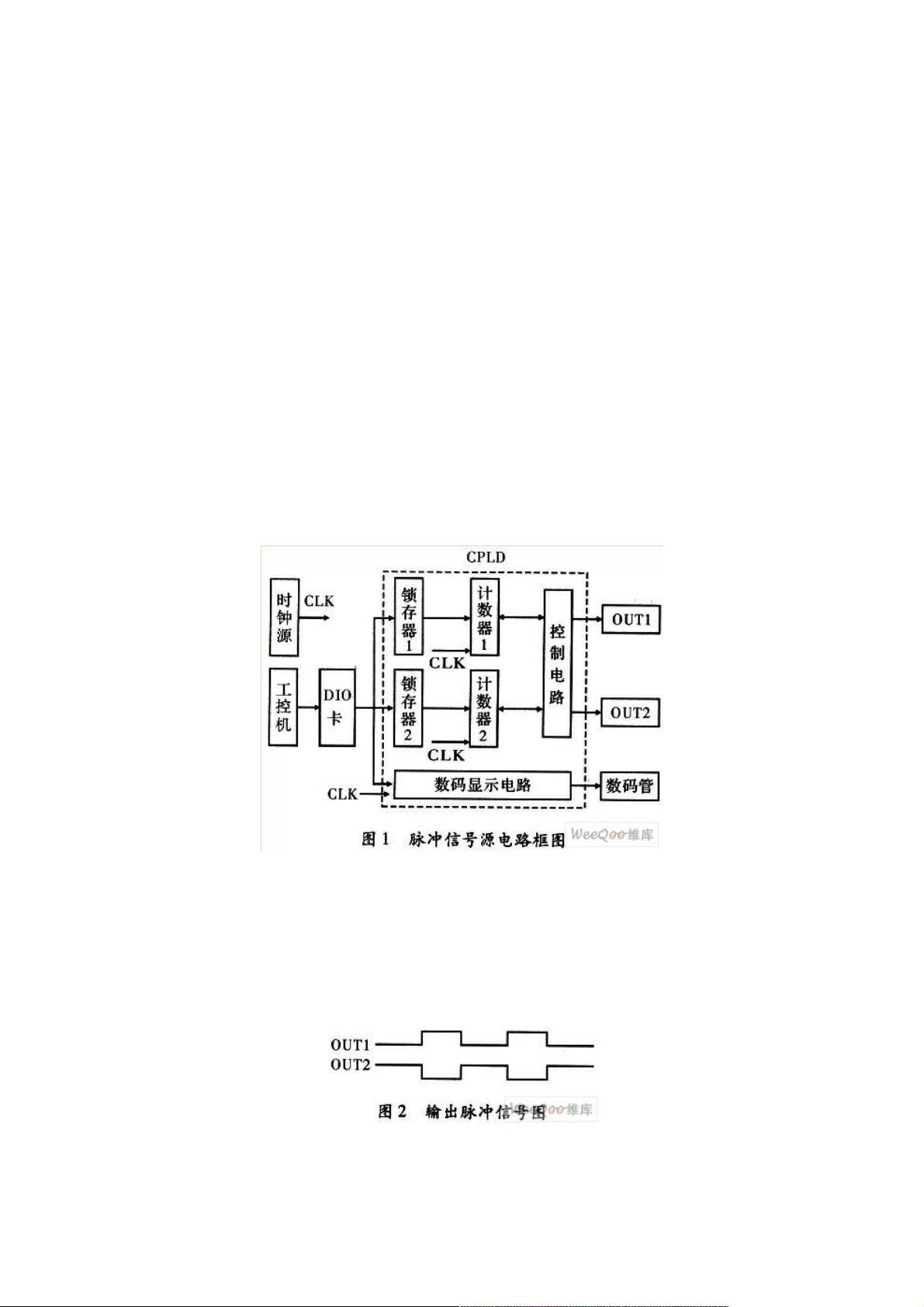

"本文介绍了一种基于CPLD(复杂可编程逻辑器件)的脉冲信号源实现方法,以克服单片机脉冲信号源在频率、步进等方面的局限性。这种CPLD脉冲信号源能实现高频率、小步进、高精度,并且参数调节灵活,易于修改。系统采用了EPM7128SLC84—10,这是Ahera公司MAX7000系列的可编程逻辑器件,具有高速、高密度和高性能特点。"

基于脉冲信号源的CPLD方法实现,主要解决了传统单片机生成脉冲信号存在的问题。通常,单片机生成的脉冲信号源受限于其内部时钟频率、执行指令的数量和周期,导致输出频率有限,步进调整范围不宽。而CPLD作为一种可编程逻辑器件,提供了更为灵活和高效的方法来生成脉冲信号。

CPLD(复杂可编程逻辑器件)在该系统中的应用,具体表现为使用EPM7128SLC84—10,这是Ahera公司MAX7000系列的成员。MAX7000系列是高密度、高性能的CMOS EPLD,其速度在工业领域内表现优异。器件内部包含多个逻辑宏单元,能够实现复杂的逻辑功能,并且具有较高的集成度和用户I/O引脚数量。此外,它还支持5.0ns的传输延迟,16位频率高达178MHz,适合高速信号处理需求。

EPM7128SLC84—10具有128个逻辑宏单元,2500个门电路,这使得它可以生成高速、精确的脉冲信号。同时,它的8个逻辑阵列块和68个L/O管脚,提供了丰富的接口能力,便于与外部设备交互。该器件的时钟频率可达147.1MHz,传输延迟为6ns,确保了信号源的快速响应。

系统的工作原理是,脉冲信号源的参数如频率和占空比由工控机通过I/O板卡进行设置,然后这些参数通过数码管进行直观显示。这种方式不仅提高了输出频率和精度,还简化了参数调整过程,使得用户可以根据需求快速修改设置。由于采用了CPLD,脉冲信号源的步进可以做得非常小,适应性强,能够满足各种精细的测试和应用需求。

基于CPLD的脉冲信号源设计,结合了硬件的优势,突破了软件实现的局限,实现了高频率、高精度、易调整的脉冲信号生成,对于需要精确控制和快速响应的系统,例如在通信、自动化、测试测量等领域,具有显著的实用价值。

2020-11-09 上传

2020-10-25 上传

2020-10-21 上传

2020-08-31 上传

2020-08-31 上传

点击了解资源详情

点击了解资源详情

2021-07-26 上传

2020-08-31 上传

weixin_38682279

- 粉丝: 9

- 资源: 889

最新资源

- ES管理利器:ES Head工具详解

- Layui前端UI框架压缩包:轻量级的Web界面构建利器

- WPF 字体布局问题解决方法与应用案例

- 响应式网页布局教程:CSS实现全平台适配

- Windows平台Elasticsearch 8.10.2版发布

- ICEY开源小程序:定时显示极限值提醒

- MATLAB条形图绘制指南:从入门到进阶技巧全解析

- WPF实现任务管理器进程分组逻辑教程解析

- C#编程实现显卡硬件信息的获取方法

- 前端世界核心-HTML+CSS+JS团队服务网页模板开发

- 精选SQL面试题大汇总

- Nacos Server 1.2.1在Linux系统的安装包介绍

- 易语言MySQL支持库3.0#0版全新升级与使用指南

- 快乐足球响应式网页模板:前端开发全技能秘籍

- OpenEuler4.19内核发布:国产操作系统的里程碑

- Boyue Zheng的LeetCode Python解答集