Cadence Virtuoso版图设计指南:构建inverter实例

需积分: 11 100 浏览量

更新于2024-07-28

收藏 853KB PDF 举报

Cadence版图设计是一种广泛应用于集成电路设计中的软件工具,它通过Virtuoso编辑器进行图形化设计,以创建电路板布局。本文档详细介绍了如何使用Cadence CDS (Cadence Design System) 的SPICE模块进行版图设计,特别是针对一个简单的非门电路为例。

第1步是建立版图文件,这涉及使用Library Manager创建一个新的库myLib。尽管前面已经提到了建立库的过程,但这里强调了在创建版图文件时的不同之处,即技术文件选项需选择"compile a new techfile"或"attach to an existing techfile",因为版图设计需要特定的技术文件支持。用户需要输入ASCIITechnologyFile中的技术文件名,例如"csmc1o0.tf"。

接下来,用户需要创建名为"inv"的单元格,包括schematic view、symbol view以及layout view。schematic view表示电路原理图,symbol view是电路符号,而layout view则是物理布局视图。在这个例子中,PMOS和NMOS的尺寸被设定为长6u和宽0.6u,模型选用的是hj3p和hj3n。

第2章主要讲解了绘制inverter掩膜版图的准备工作。首先在Library Manager中打开"inv"的layout view,进入Virtuoso编辑窗口,如图2-2-1所示。这个界面分为Iconmenu(图标菜单)、menubanner(菜单栏)和status banner(状态栏)三部分,提供了一系列用于版图编辑的工具和快捷键。例如,ZoomIn用于放大视图,Zoomoutby2用于缩小视图两倍,Save则是保存当前设计。

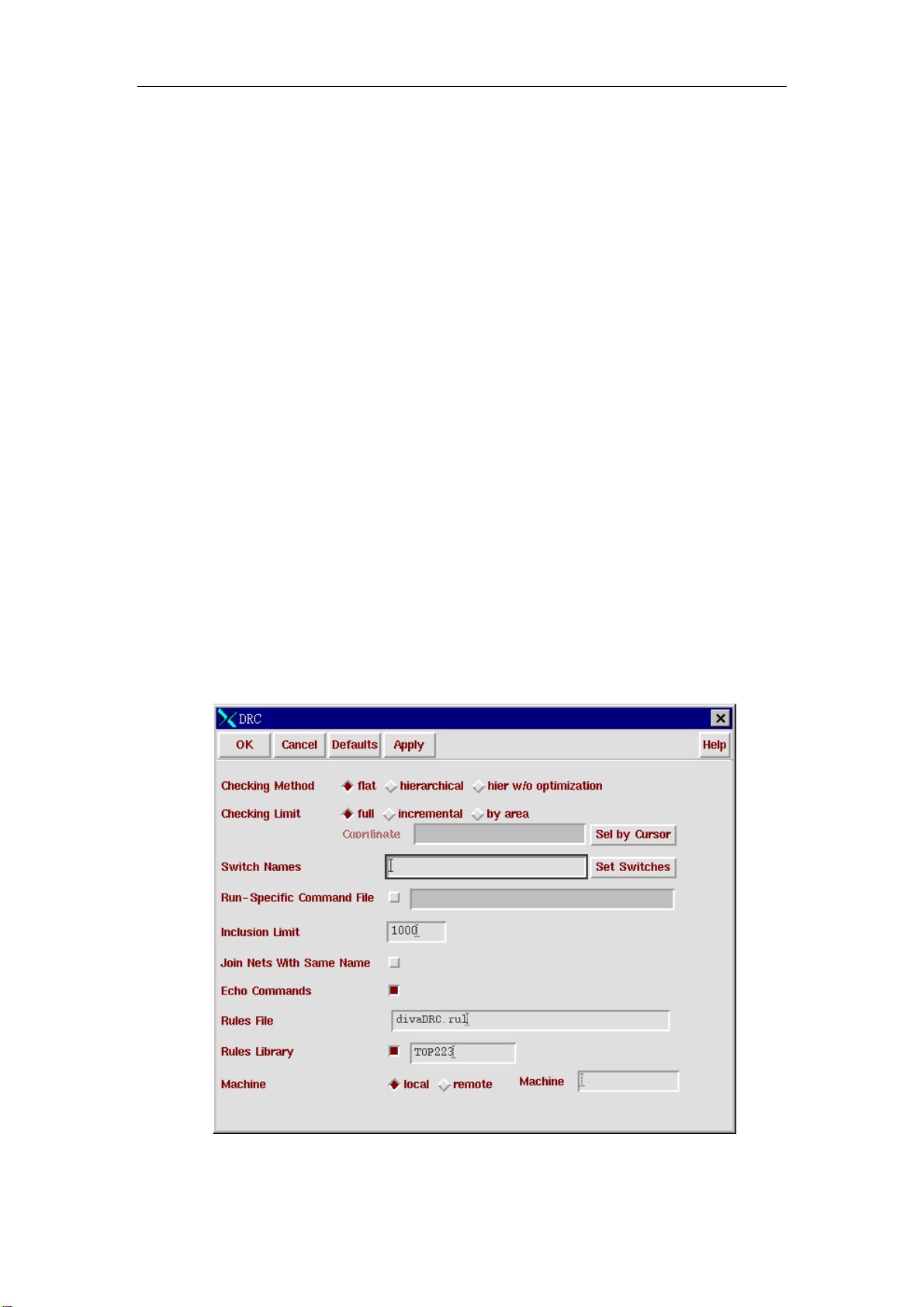

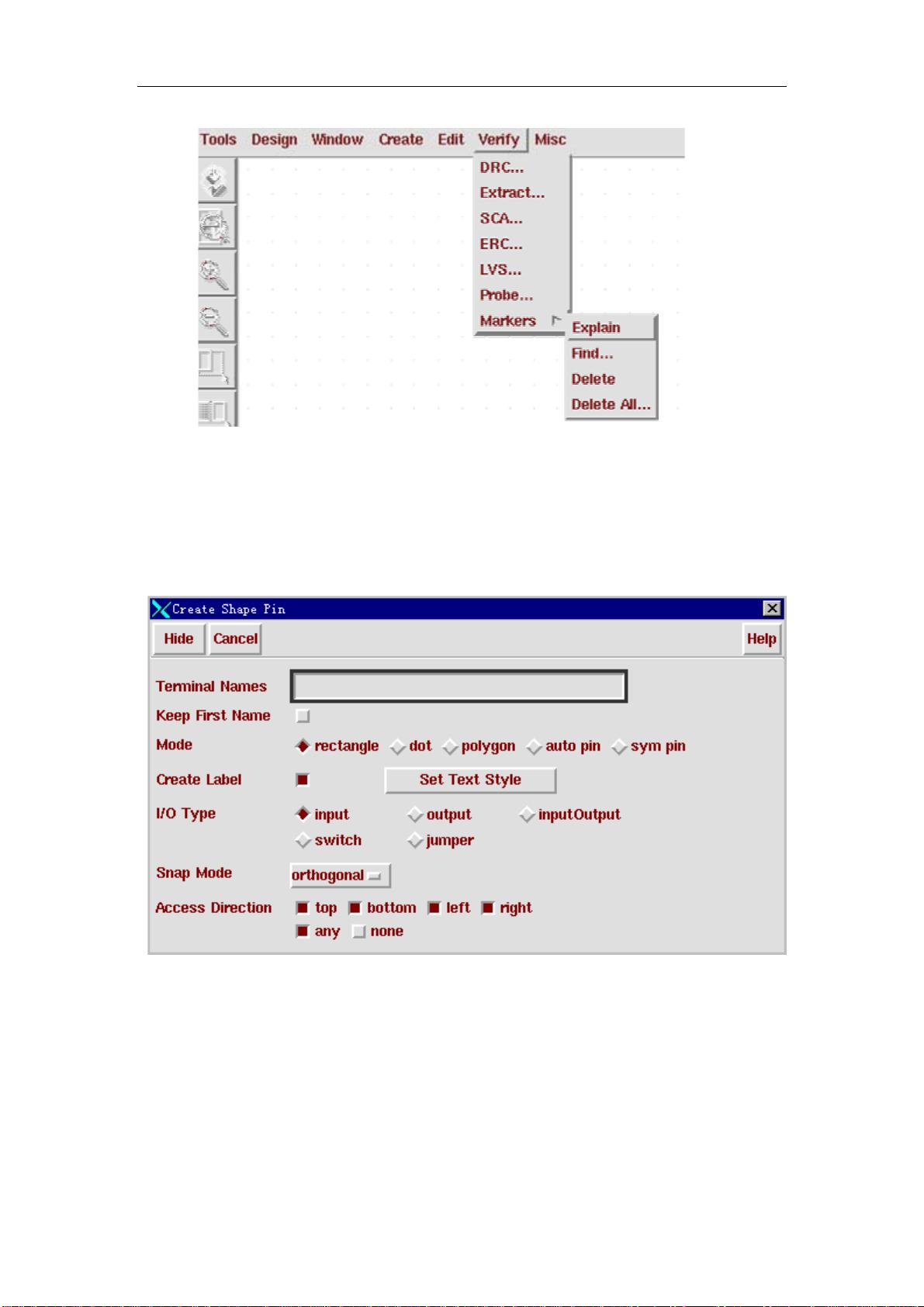

在实际操作中,用户会利用这些工具和快捷键来精确地绘制晶体管、布线、焊盘等元件,并进行布局调整,确保电路的功能性和制造可行性。Cadence CDS SPICE的使用说明还包括了对其他高级功能的介绍,比如设计规则检查、DRC(Design Rule Checking,设计规则检查)和LVS(Layout Versus Schematic,布局对齐与原理图对比)等,这些都是版图设计过程中必不可少的步骤。

Cadence版图设计是一个复杂且精细的过程,熟练掌握Virtuoso编辑器的操作技巧,对于电路设计人员来说至关重要。通过理解并应用这份教程,用户能够有效地创建、优化和验证复杂的集成电路版图,以满足现代电子设备对小型化、高性能的需求。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2008-12-11 上传

2012-12-17 上传

2014-05-18 上传

2010-03-20 上传

2011-09-08 上传

2010-02-03 上传

xl46512c

- 粉丝: 2

- 资源: 68

最新资源

- 火炬连体网络在MNIST的2D嵌入实现示例

- Angular插件增强Application Insights JavaScript SDK功能

- 实时三维重建:InfiniTAM的ros驱动应用

- Spring与Mybatis整合的配置与实践

- Vozy前端技术测试深入体验与模板参考

- React应用实现语音转文字功能介绍

- PHPMailer-6.6.4: PHP邮件收发类库的详细介绍

- Felineboard:为猫主人设计的交互式仪表板

- PGRFileManager:功能强大的开源Ajax文件管理器

- Pytest-Html定制测试报告与源代码封装教程

- Angular开发与部署指南:从创建到测试

- BASIC-BINARY-IPC系统:进程间通信的非阻塞接口

- LTK3D: Common Lisp中的基础3D图形实现

- Timer-Counter-Lister:官方源代码及更新发布

- Galaxia REST API:面向地球问题的解决方案

- Node.js模块:随机动物实例教程与源码解析