Verilog设计与验证实战指南

"《Verilog设计与验证》是一本深入探讨Verilog HDL设计与验证技术的专业书籍,适合电子、通信、半导体行业的研发人员学习。该书由EDA先锋工作室创作,成员均为行业资深专家,他们在EDA专业论坛提供长期的技术支持和答疑服务。书中内容涵盖了Verilog的基础语法、设计方法、验证流程、不同设计层次、RTL建模以及同步设计原则等,旨在帮助读者快速掌握Verilog HDL在IC设计中的实际应用。"

本书针对Verilog HDL的使用现状,指出目前市场上的相关书籍多侧重于语法和建模,而缺乏理论与实践的结合。因此,该书特别强调了理论与实用性并重,旨在为读者提供全面而深入的学习体验。

第1章,书中首先阐述了HDL设计的基本方法,对比了Verilog与VHDL、C等语言的差异,同时详细解析了HDL语言在设计和验证过程中的步骤和流程。

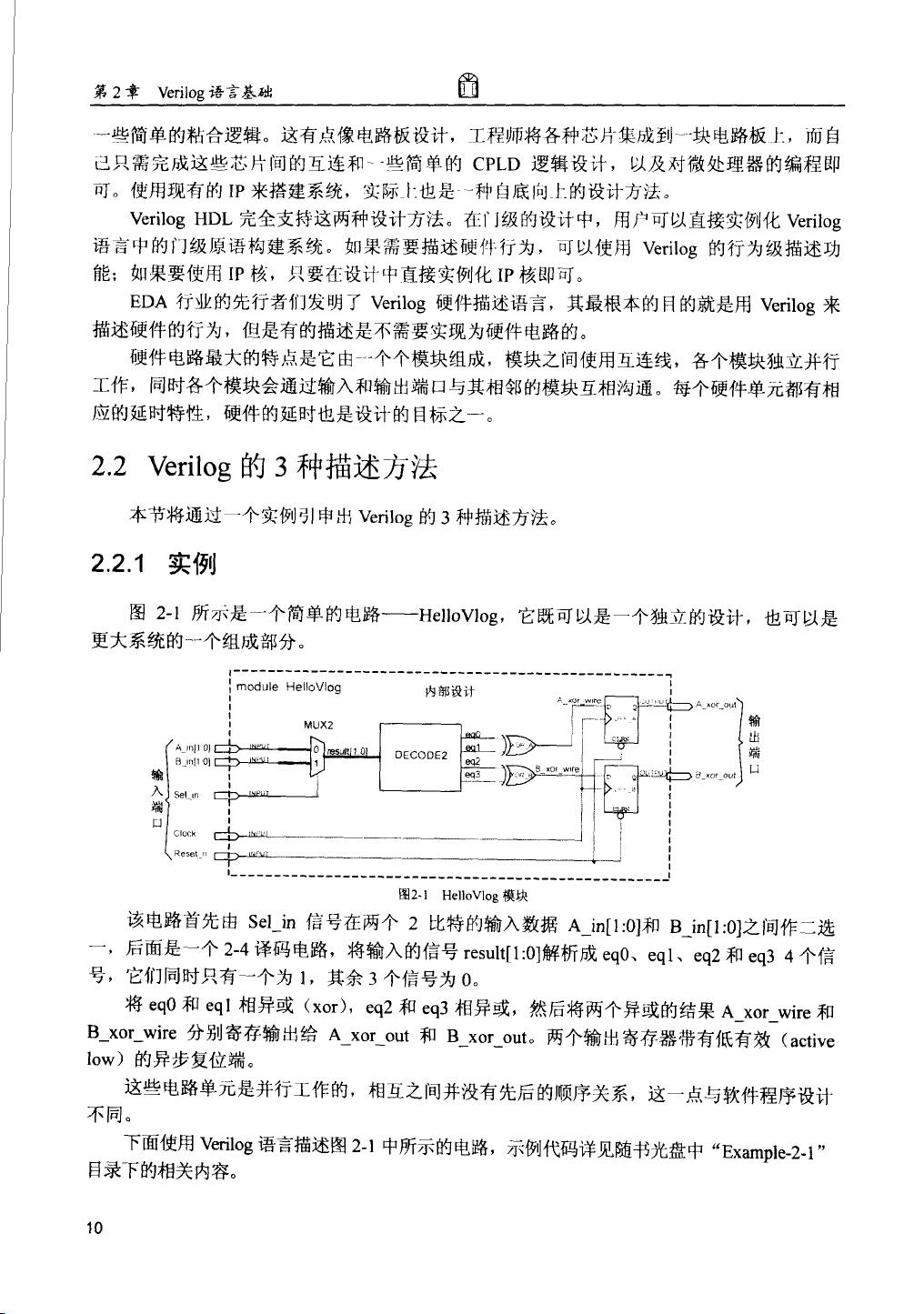

第2章则详细讲解了Verilog的基础语法,这是理解Verilog设计的基础,包括变量定义、运算符、控制结构等核心概念。

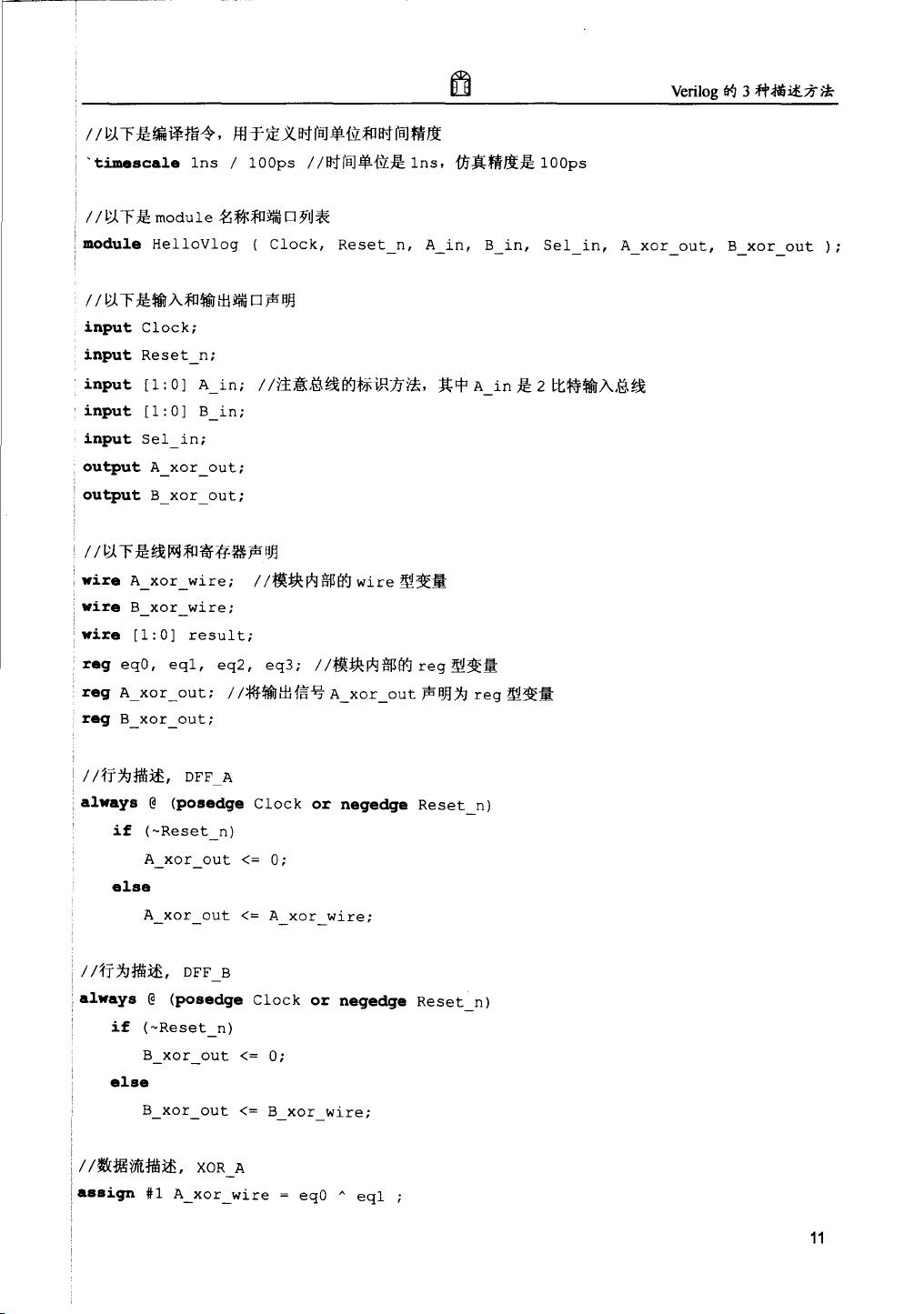

第3章深入介绍了Verilog的3种描述方法(行为描述、数据流描述、门级描述)以及不同的设计层次,帮助读者理解和掌握从高层次抽象到低层次实现的设计思路。

第4章聚焦于RTL(Register Transfer Level)建模,解释了其基本概念,并通过实例展示了如何用Verilog设计常见电路,同时引出了可综合子集的概念,这对于实际芯片设计至关重要。

第5章则总结了RTL同步设计的关键原则,包括如何划分设计模块、处理组合逻辑和时序逻辑,以及优化RTL代码的策略,这些都是提升设计效率和质量的关键。

第6章至第9章(未完全列出)可能继续深入讨论验证技术、系统级设计、测试平台(testbench)的构建等高级主题,为读者提供完整的Verilog设计与验证知识体系。

此外,读者可以通过EDA先锋工作室设立的在线论坛获取额外的支持和资源,与业界专业人士交流,提升自身技能。该书还提供了配套的电子资源下载,方便读者进行实践操作和进一步学习。

《Verilog设计与验证》是一本针对Verilog HDL初学者和有一定基础的工程师的理想教材,它将理论教学与实践经验相结合,旨在帮助读者在快速发展的IC设计行业中立足并发展。

2009-12-07 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

2015-05-26 上传

nbucxl

- 粉丝: 0

- 资源: 4

最新资源

- 前端协作项目:发布猜图游戏功能与待修复事项

- Spring框架REST服务开发实践指南

- ALU课设实现基础与高级运算功能

- 深入了解STK:C++音频信号处理综合工具套件

- 华中科技大学电信学院软件无线电实验资料汇总

- CGSN数据解析与集成验证工具集:Python和Shell脚本

- Java实现的远程视频会议系统开发教程

- Change-OEM: 用Java修改Windows OEM信息与Logo

- cmnd:文本到远程API的桥接平台开发

- 解决BIOS刷写错误28:PRR.exe的应用与效果

- 深度学习对抗攻击库:adversarial_robustness_toolbox 1.10.0

- Win7系统CP2102驱动下载与安装指南

- 深入理解Java中的函数式编程技巧

- GY-906 MLX90614ESF传感器模块温度采集应用资料

- Adversarial Robustness Toolbox 1.15.1 工具包安装教程

- GNU Radio的供应商中立SDR开发包:gr-sdr介绍