Vivado设计套件:FPGA/自适应SoC I/O和时钟规划指南

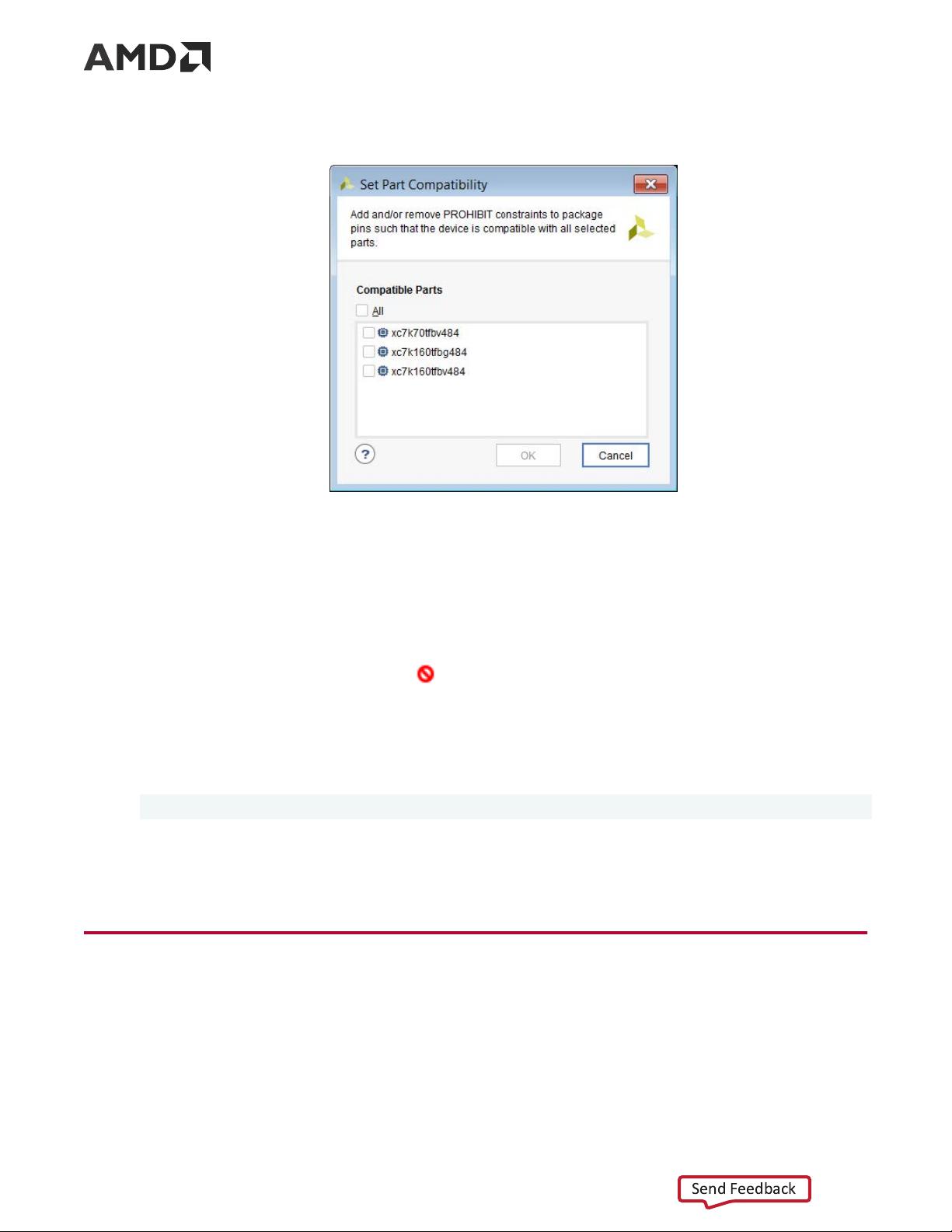

"Xilinx FPGA UG 899 - I/O和时钟规划是FPGA/自适应SoC设计中的重要环节,涉及到信号布局、信号完整性和电源管理等多个方面。该文档是Vivado Design Suite用户指南,针对2023.1版本,旨在帮助设计者优化设计流程,处理PCB与FPGA之间的交互,以及适应不断变化的行业标准。" 在FPGA开发过程中,I/O和时钟规划是至关重要的步骤,它决定了设计的性能和可靠性。这份用户指南详细阐述了以下几个关键知识点: 1. **I/O规划**:设计者需要考虑如何将不同类型的信号分配到FPGA的物理引脚上,以减少信号路径长度和交叉,从而提高信号完整性和降低电磁干扰。对于高速信号,必须特别注意确保其完整性,避免信号失真和反射。 2. **时钟规划**:时钟是数字系统的心跳,正确的时钟分配能保证系统定时正确,防止时序违规。设计者需要考虑时钟网络的延迟,以及时钟源的分布和同步,以满足设计的时序约束。 3. **电源和接地**:良好的电源和接地规划是保证信号完整性和降低噪声的关键。设计者需要评估PCB上的电源和接地信号的可用性,并根据需求规划去耦电容,确保稳定供电和低阻抗返回路径。 4. **兼容性**:在I/O规划中,需要考虑设备可能的配置,使其能与备用设备协同工作,增加设计的灵活性和可扩展性。 5. **PCB设计**:设计者需协调PCB设计者的需求,确保信号布线的简洁性和高效性,同时避免信号路径间的干扰。 6. **设备编程和调试**:规划阶段需要识别设备的编程和调试接口,确保这些功能在实际操作中能够顺利进行。 7. **非包容性语言更新**:AMD Adaptive Computing正在逐步移除产品和相关资料中的非包容性语言,以创造一个更包容的工作环境和用户体验。 本指南按照设计流程组织内容,涵盖了从基础概念到具体技术实施的各个阶段,包括使用Platform Board Flow进行I/O和时钟规划的方法,对不同技术(如SSIT,Zynq UltraScale+ MPSoCs,UltraScale和UltraScale+,以及Versal Adaptive SoC)的特定I/O规划策略,以及配置设备的细节等。 通过深入阅读和理解这份用户指南,FPGA和系统设计者可以更好地规划他们的设计,优化性能,减少潜在问题,并与最新的行业标准保持一致。

剩余113页未读,继续阅读

- 粉丝: 5648

- 资源: 89

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- 新型矿用本安直流稳压电源设计:双重保护电路

- 煤矿掘进工作面安全因素研究:结构方程模型

- 利用同位素位移探测原子内部新型力

- 钻锚机钻臂动力学仿真分析与优化

- 钻孔成像技术在巷道松动圈检测与支护设计中的应用

- 极化与非极化ep碰撞中J/ψ的Sivers与cos2φ效应:理论分析与COMPASS验证

- 新疆矿区1200m深孔钻探关键技术与实践

- 建筑行业事故预防:综合动态事故致因理论的应用

- 北斗卫星监测系统在电网塔形实时监控中的应用

- 煤层气羽状水平井数值模拟:交替隐式算法的应用

- 开放字符串T对偶与双空间坐标变换

- 煤矿瓦斯抽采半径测定新方法——瓦斯储量法

- 大倾角大采高工作面设备稳定与安全控制关键技术

- 超标违规背景下的热波动影响分析

- 中国煤矿选煤设计进展与挑战:历史、现状与未来发展

- 反演技术与RBF神经网络在移动机器人控制中的应用

信息提交成功

信息提交成功