IDT71V30S/L:高性能3.3V双口静态RAM芯片详解

"IDT71V30S/L是一款高速3.3V 1Kx8双口静态RAM芯片,由Integrated Device Technology, Inc.制造。这款芯片提供了高速访问速度,低功耗操作,以及内置的端口仲裁逻辑和中断标志,适用于需要高效数据交换和同步的系统。"

IDT双口RAM芯片IDT71V30S/L是专为高性能和低功耗设计的一款存储解决方案。其主要特点包括:

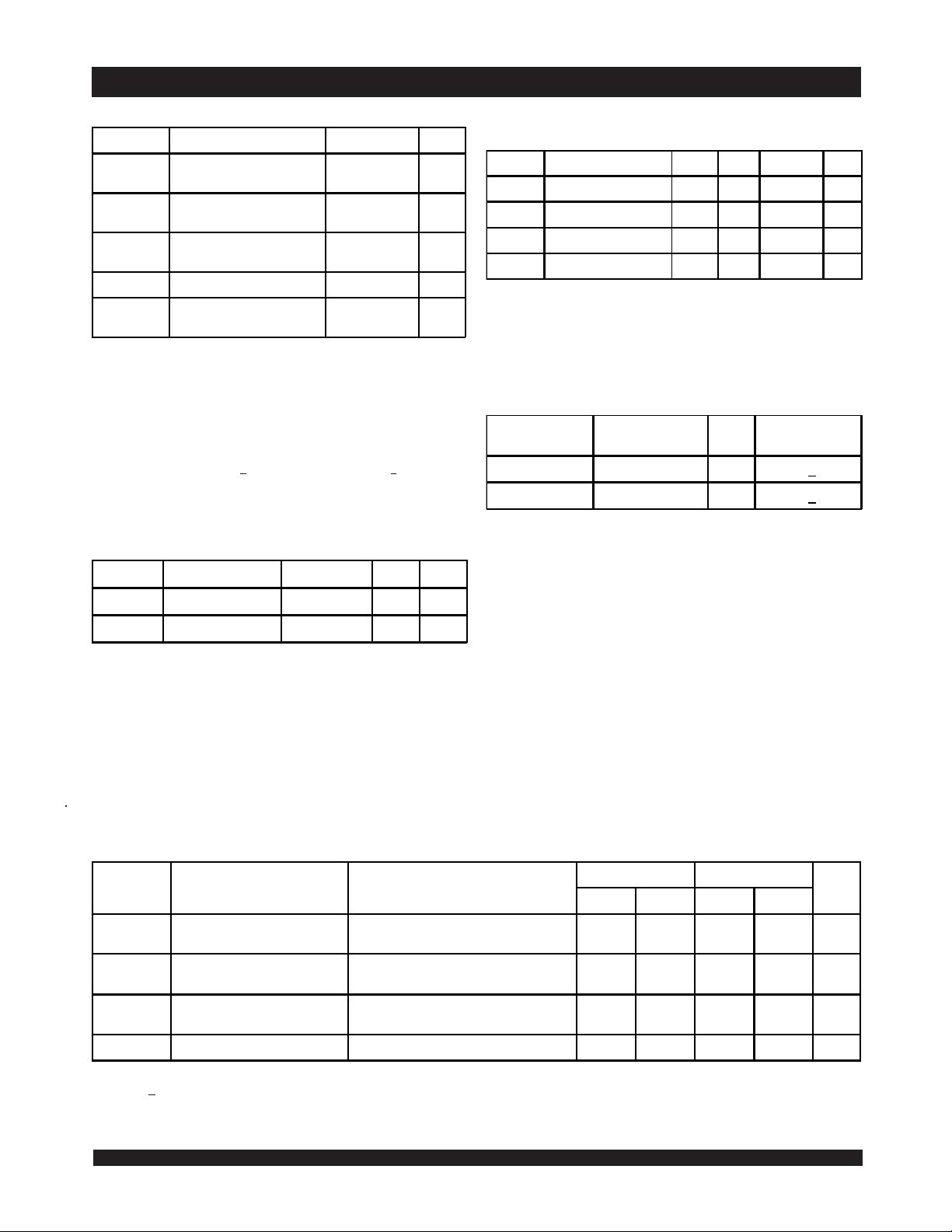

1. 高速访问:商业应用下,最大访问速度分别为25/35/55ns,这使得它在处理大量数据时能快速响应。

2. 低功耗:IDT71V30S在活动模式下典型功耗为375mW,待机模式下仅为5mW。IDT71V30L在相同条件下,待机功耗进一步降低至1mW,适合对电源效率有高要求的应用。

3. 内置功能模块:芯片内集成了端口仲裁逻辑,可以有效地解决两个端口同时访问内存时的冲突问题。此外,还有中断标志功能,支持端口间的通信。

4. 完全异步操作:从任一端口都能实现完全异步操作,确保了不同时钟域下的稳定数据传输。

5. 电池备份操作:2V数据保留功能(仅限LOnly),即使在主电源断开时也能保持数据完整性。

6. 兼容性:采用TTL兼容的单3.3V±0.3V电源供电,简化了系统集成。

7. 工业温度范围:部分速度等级支持-40℃到+85℃的工业级工作温度,扩大了应用领域。

8. 环保选项:提供绿色零件,符合订购信息中的环保要求。

该芯片的内部结构包括I/O控制、地址解码器、存储阵列、仲裁和中断逻辑等关键组件。其中,I/O控制负责数据输入输出,地址解码器根据提供的地址信号选择内存单元,仲裁和中断逻辑则处理端口之间的访问冲突和通信中断。

在实际应用中,用户可以通过R/WL、CEL、OEL等控制信号进行读写操作,而BUSY输出和INT输出则提供状态指示。例如,BUSY信号表示当前芯片正在进行操作,INT则用于中断请求。另外,I/O0L-I/O7L和I/O0R-I/O7R代表两个端口的数据输入输出引脚,A9L、A0L、A9R、A0R为地址线,用于指定要访问的内存位置。R/WR、CER、OER则是读写控制、片选输出和输出使能信号。

IDT71V30S/L双口RAM芯片以其高速、低功耗和丰富的功能特性,适用于需要高效数据交换和同步的系统,如嵌入式系统、通信设备、多处理器环境等。其灵活的设计和广泛的温度适应性使其在各种工业和商业应用中都有广泛的应用前景。

2011-08-14 上传

2022-09-23 上传

2011-06-25 上传

2011-12-12 上传

2021-07-26 上传

2012-01-07 上传

点击了解资源详情

fydb1985

- 粉丝: 2

- 资源: 16

最新资源

- Fisher Iris Setosa数据的主成分分析及可视化- Matlab实现

- 深入理解JavaScript类与面向对象编程

- Argspect-0.0.1版本Python包发布与使用说明

- OpenNetAdmin v09.07.15 PHP项目源码下载

- 掌握Node.js: 构建高性能Web服务器与应用程序

- Matlab矢量绘图工具:polarG函数使用详解

- 实现Vue.js中PDF文件的签名显示功能

- 开源项目PSPSolver:资源约束调度问题求解器库

- 探索vwru系统:大众的虚拟现实招聘平台

- 深入理解cJSON:案例与源文件解析

- 多边形扩展算法在MATLAB中的应用与实现

- 用React类组件创建迷你待办事项列表指南

- Python库setuptools-58.5.3助力高效开发

- fmfiles工具:在MATLAB中查找丢失文件并列出错误

- 老枪二级域名系统PHP源码简易版发布

- 探索DOSGUI开源库:C/C++图形界面开发新篇章